Unit - I

### SINGLE STAGE AMPLIFIERS

# Outline – Part II

- Noise in analog ICs

- Matching in analog ICs

- Operational Amplifier design examples

- Analog design methodology

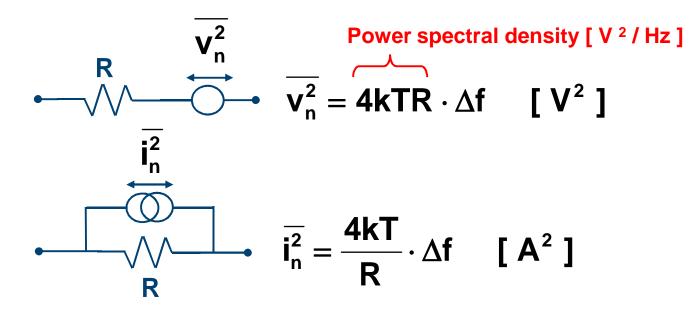

### Thermal noise in passive components

# Thermal noise is caused by the random thermally excited vibration of the charge carriers in a conductor.

There are no sources of noise in ideal capacitors or inductors. In practice, real components have parasitic resistance that does display thermal noise!

### Noise sources in MOS transistors

**Channel thermal noise:** due to the random thermal motion of the carriers in the channel

**1/f noise:** due to the random trapping and detrapping of mobile carriers in the traps located at the Si-SiO<sub>2</sub> interface and within the gate oxide.

**Bulk resistance thermal noise:** due to the distributed substrate resistance.

Gate resistance thermal noise: due to the resistance of the polysilicon gate and of the interconnections.

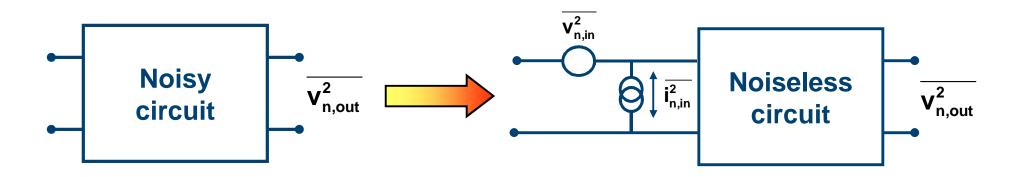

### Noise in circuits

To be independent from the gain of a given system, we use the concept of input-referred noise. This allows comparing easily the noise performance of different circuits (with different gains), and calculating easily the Signal-to-Noise Ratio (SNR).

At the input of our linear two-port circuit, we use two noise generator (one noise voltage source and one noise current source) to represent the noise of the system regardless the impedance at the input of the circuit and of the source driving the circuit.

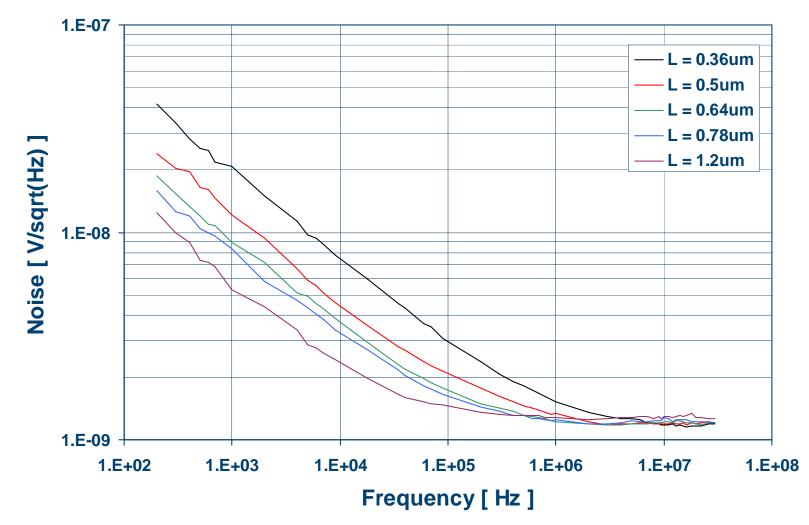

### Input-referred voltage noise

The MOS transistor is represented by its small-signal equivalent circuit. We can refer the noise sources inside the MOS transistor to the input, obtaining an input-referred voltage noise.

$\gamma$  ideally varies from 1/2 (w.i.) to 2/3 (s.i.)

K<sub>a</sub> = 1/f noise parameter, technology dependent

Usually, the first two terms are the most important

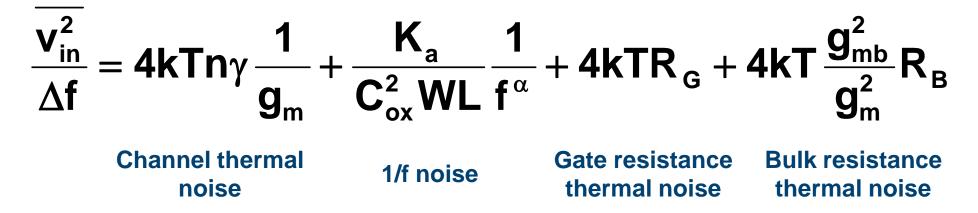

### N-channel noise spectra

$W = 2 \text{ mm}, I_{DS} = 0.5 \text{ mA}, V_{DS} = 0.8 \text{ V}, V_{BS} = 0 \text{ V}$

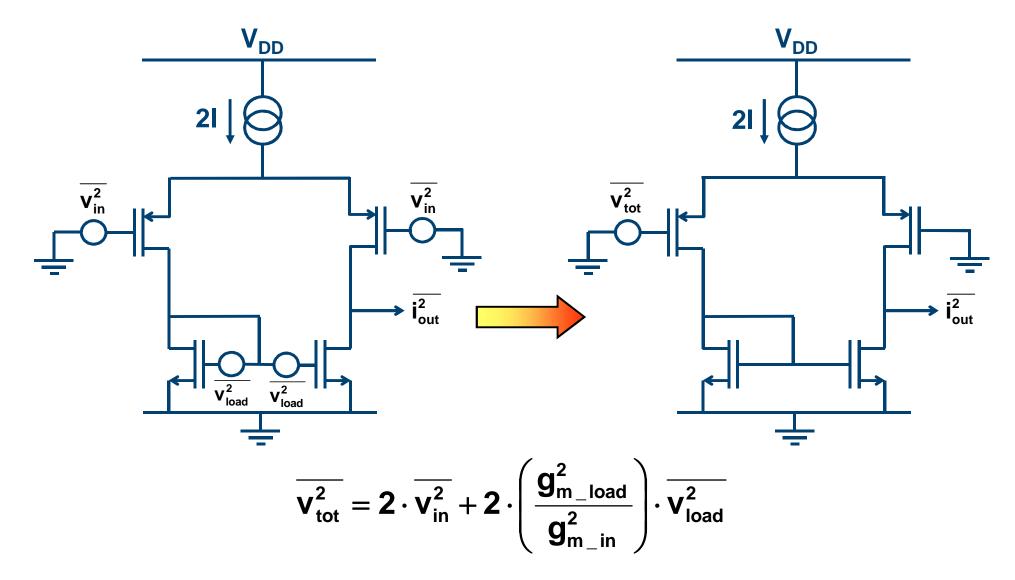

### Noise in a DP + Active CM

### Noise in a DP + Active CM

## Outline – Part II

- Noise in analog ICs

- Matching in analog ICs

- Operational Amplifier design examples

- Analog design methodology

### The importance of matching

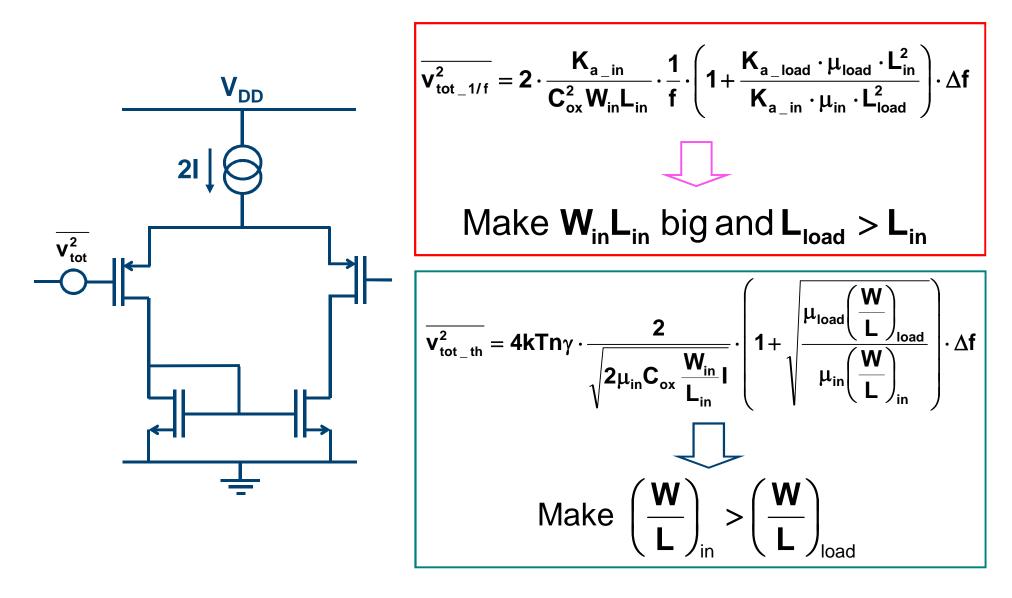

# Yield of an N-bit flash Analog-to-Digital converter as a function of the comparator mismatch

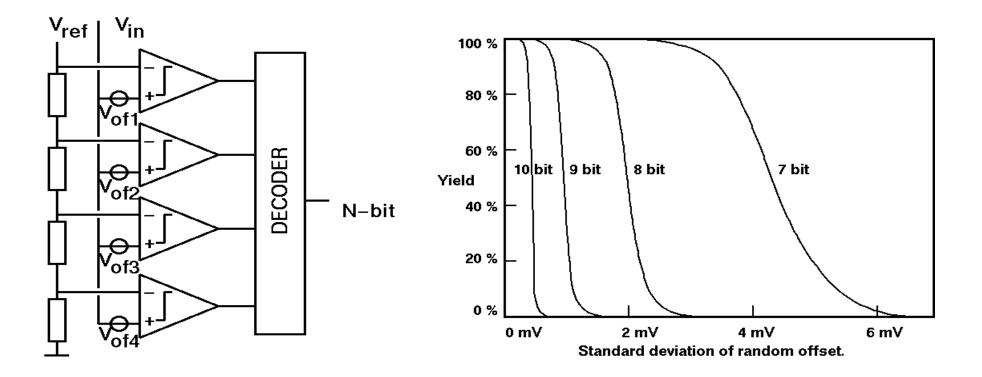

### Relative & absolute mismatch

# Mismatch occurs for all IC components (resistors, capacitors, bipolar and MOS transistors)

$$\frac{\Delta L}{L} = 200 \cdot \frac{L2 - L1}{L2 + L1}$$

[%]

### **Relative mismatch**

$\Delta \textbf{D} = \Delta \textbf{D1} - \Delta \textbf{D2} \quad [\mu m]$

### **Absolute mismatch**

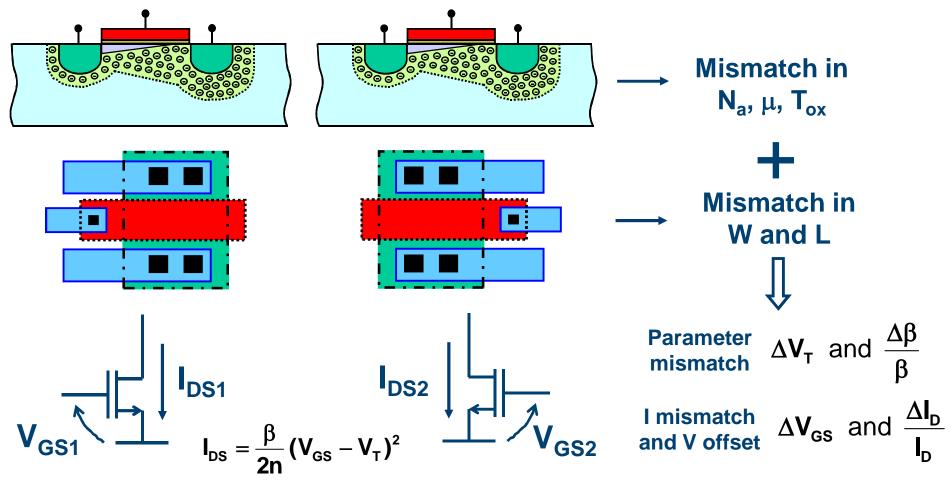

### Mismatch in MOS transistors

Mismatch in physical parameters (N<sub>a</sub>,  $\mu$ , T<sub>ox</sub>) and layout dimensions (W, L) gives origin to mismatch in electrical parameters (V<sub>T</sub>,  $\beta$  and therefore I<sub>D</sub>)

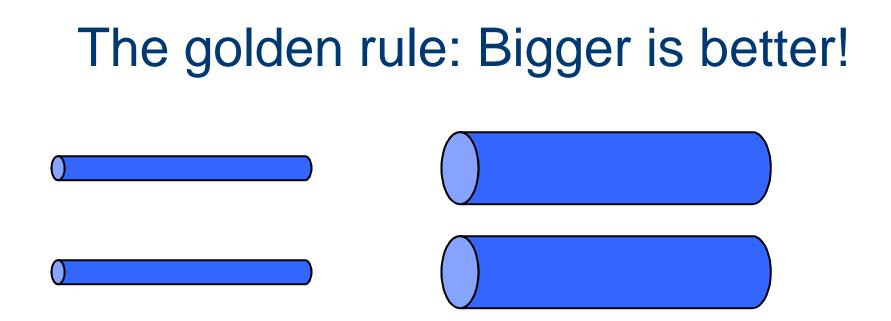

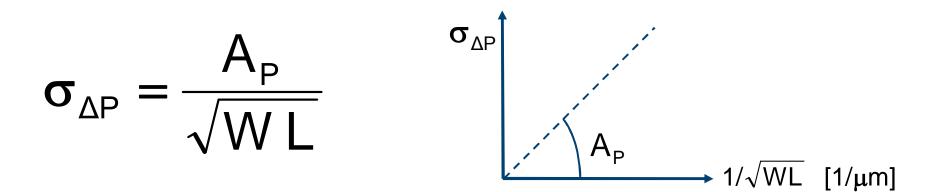

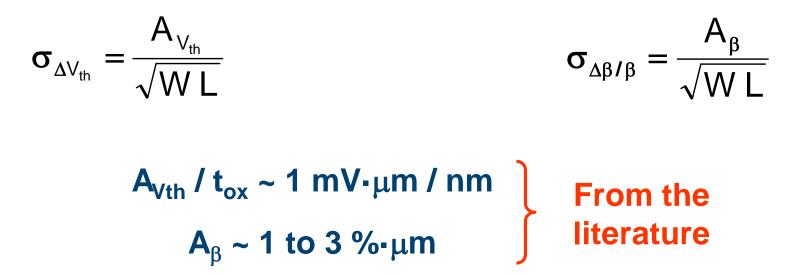

Random effects "average out" better if the area is bigger. Therefore, for a given parameter P, we expect something like

### **Expected mismatch**

Usually in a pair of identical transistors the two most important parameter subject to mismatch are the threshold voltage  $V_{th}$  and the current factor  $\beta$

Mismatch can be treated as another source of noise. As in the noise case, different "mismatch" sources can be grouped into one adding the variances (not the standard deviations)

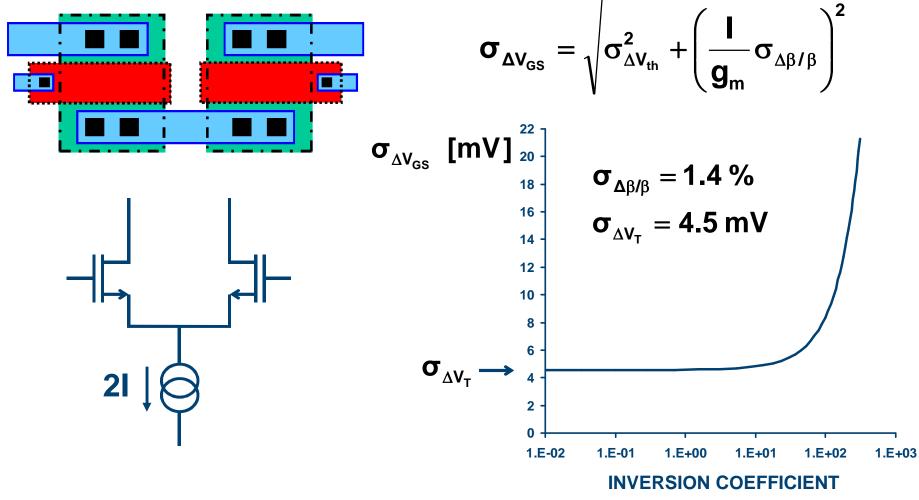

### **Differential pair mismatch**

### The two transistors have the same drain current

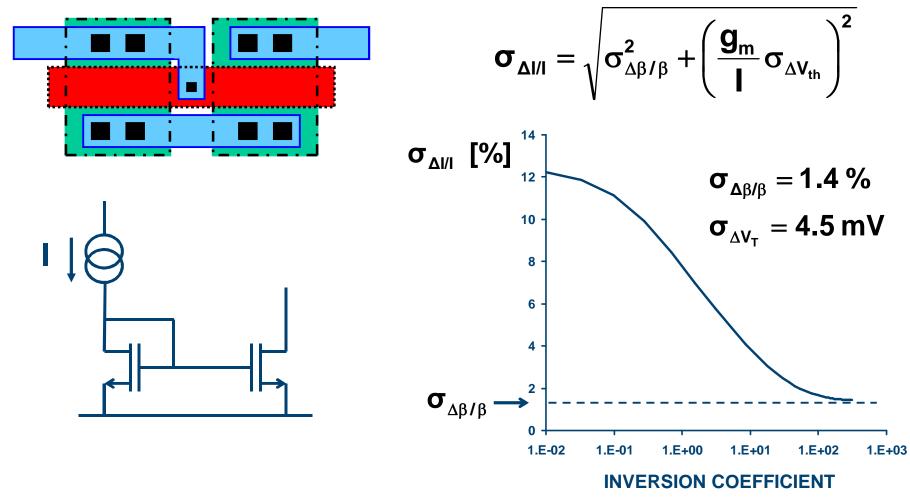

### Current mirror mismatch

### The two transistors have the same gate voltage

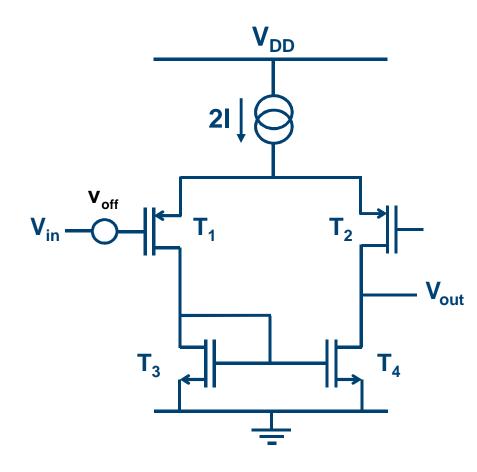

### Offset of a DP + Active CM

#### **RANDOM OFFSET (WORST CASE)**

$$\mathbf{v}_{\mathsf{off}} = \Delta \mathbf{V}_{\mathsf{T}1,2} + \frac{\mathbf{I}}{\mathbf{g}_{\mathsf{m}1,2}} \left( \frac{\Delta \beta_{\mathsf{1},2}}{\beta_{\mathsf{1},2}} + \frac{\Delta \beta_{\mathsf{3},4}}{\beta_{\mathsf{3},4}} + \frac{\mathbf{g}_{\mathsf{m}3,4}}{\mathbf{I}} \Delta \mathbf{V}_{\mathsf{T}3,4} \right)$$

#### SYSTEMATIC OFFSET

The difference in the drain voltages of T1 and T2 gives origin a difference in the DC currents in the two branches.

#### **"COMMON MODE" OFFSET**

Due to mismatches in the transistors, a common mode signal at the input gives a non zero output voltage signal.

# Outline – Part II

- Noise in analog ICs

- Matching in analog ICs

- Operational Amplifier design examples

- Op Amp application examples

- Single-Stage Op Amps

- Two-Stage Op Amps

- Fully Differential Op Amps

- Feedback and frequency compensation

- Analog design methodology

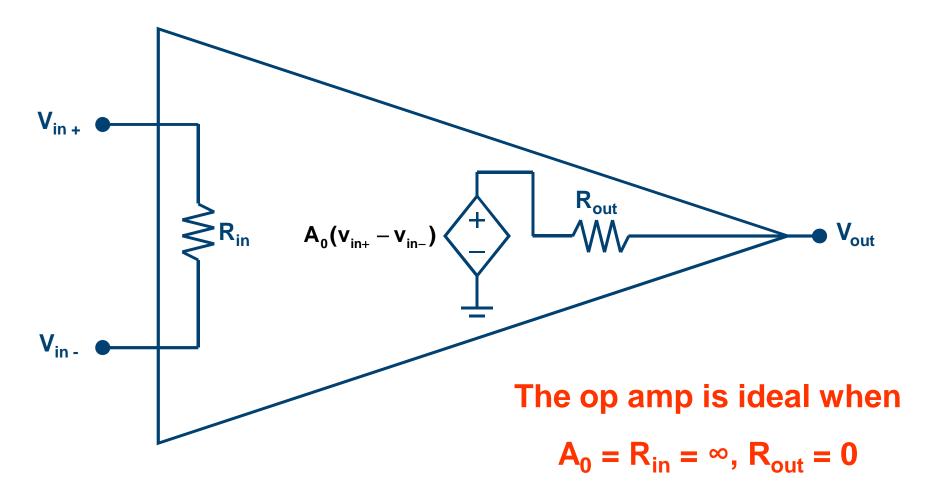

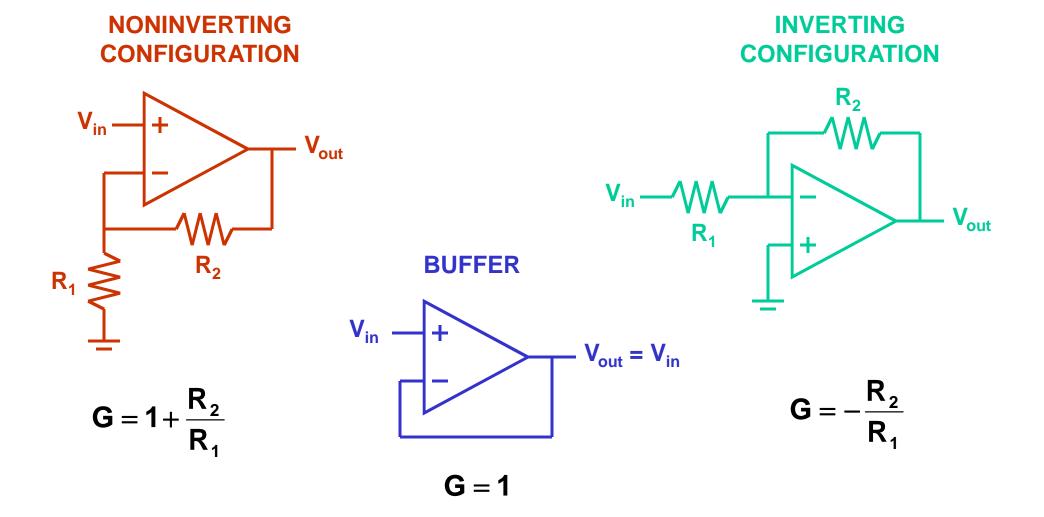

### The ideal op amp

An op amp is basically a voltage-controlled voltage source

### Op amp application examples

The above equations are valid only if the gain  $A_0$  of the op amp is very high!

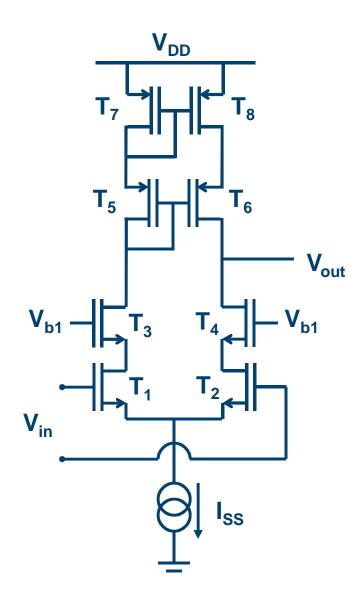

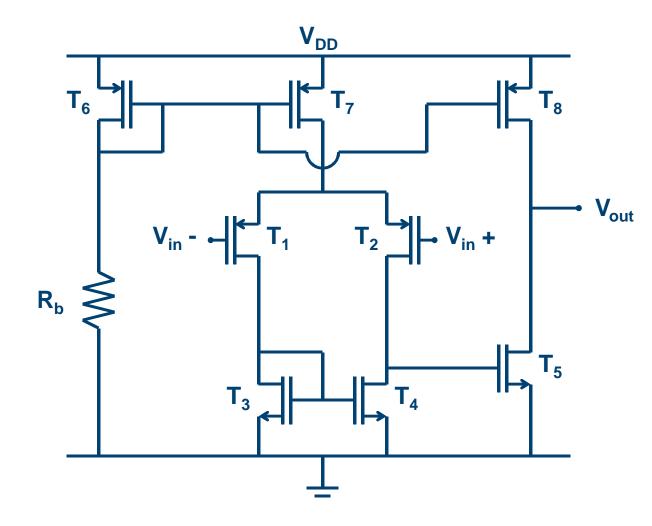

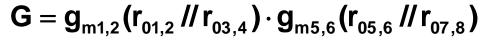

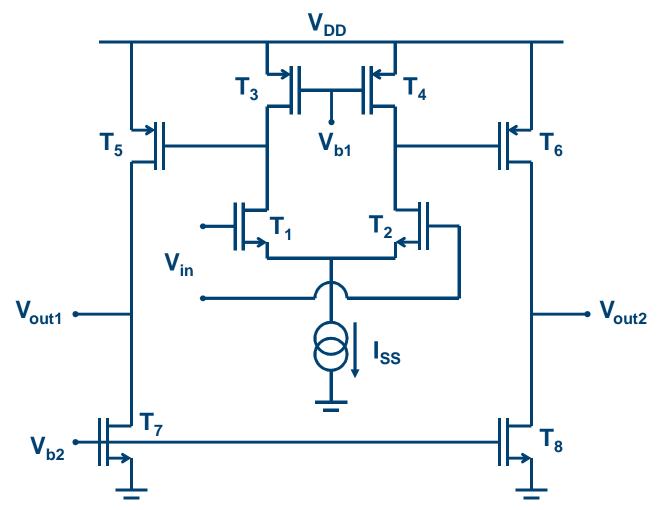

## Single-stage Op Amp

The differential pair + active current mirror scheme we have already seen is a single stage op amp. Several different solutions can be adopted to make a Single-stage amplifier. If high gains are needed, we can use, for example, cascode structures.

With single-stage amplifiers it is difficult to obtain at the same time high gain and voltage excursion, especially when other characteristics are also required, such as speed and/or precision.

Two-stage configurations in this sense are better, since they decouple the gain and voltage swing requirements.

### Two-stage Op Amp

$$\mathbf{G} = \mathbf{g}_{m2}(\mathbf{r}_{02} \, / \! / \, \mathbf{r}_{04}) \cdot \mathbf{g}_{m5}(\mathbf{r}_{05} \, / \! / \, \mathbf{r}_{08})$$

The second stage is very often a CSS, since this allows the maximum voltage swing. The output voltage swing in this case is V<sub>DD</sub> - |2V<sub>DS\_SAT</sub>|

### Two-stage Op Amp

$$\mathbf{G} = \mathbf{g}_{m1,2}(\mathbf{r}_{01,2} \, / / \, \mathbf{r}_{03,4}) \cdot \mathbf{g}_{m6}(\mathbf{r}_{06} \, / / \, \mathbf{r}_{08})$$

In this case we kept the differential behavior of the first stage, and is the current mirror T7-T8 which does the differential-to-single ended conversion. The output is still a CSS.

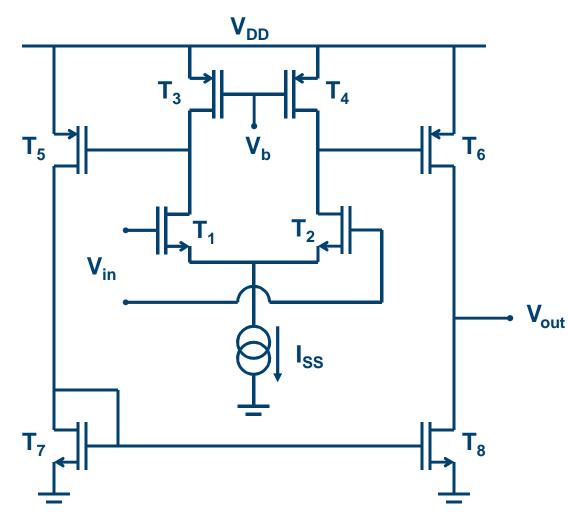

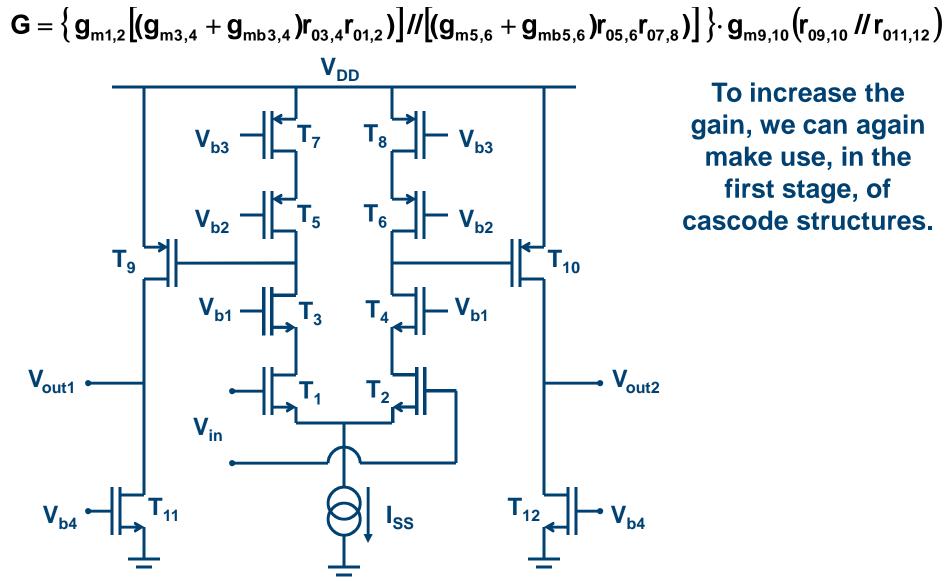

### **Fully Differential Op Amp**

### Fully Differential Op Amp

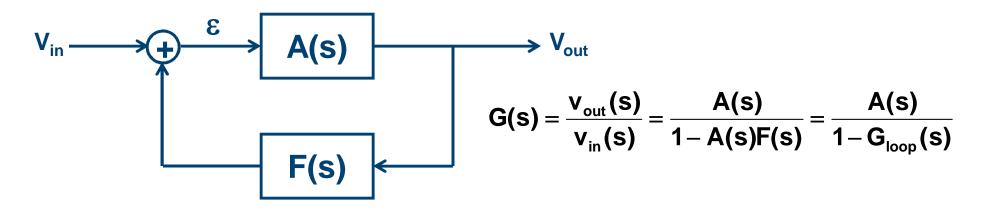

### Feedback

- A(s) is the open loop transfer function

- F(s) is the feedback network transfer function

- G(s) is the closed loop transfer function

- A(s)F(s) is the loop gain

- If the feedback is negative, the loop gain is negative

• For

$$|G_{loop}(s)| >> 1$$

, we have that  $G(s) = -\frac{1}{F(s)}$

### Properties of negative feedback

**Negative** feedback reduces substantially the gain of a circuit, but it improves several other characteristics:

• Gain desensitization: the open loop transfer function is generally dependent on many varying quantities, given by the active components in the circuit. Using a passive feedback network, we can reduce the dependence of the gain variation on the variations of the open loop transfer function.

$$\frac{\mathrm{dG}}{\mathrm{G}} = \frac{\mathrm{dA}}{\mathrm{A}} \frac{1}{1 - \mathrm{G}_{\mathrm{loop}}}$$

Reduction of nonlinear distortion

• Reduction or increase (depending on the feedback topology) of the input and output impedances by a factor 1-G<sub>loop</sub>.

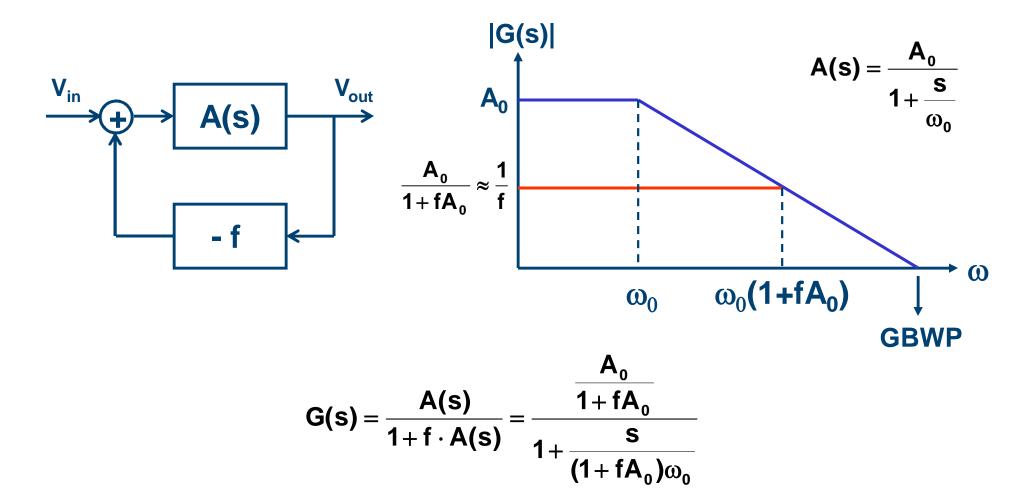

Increase of the bandwidth

### **Bode diagrams**

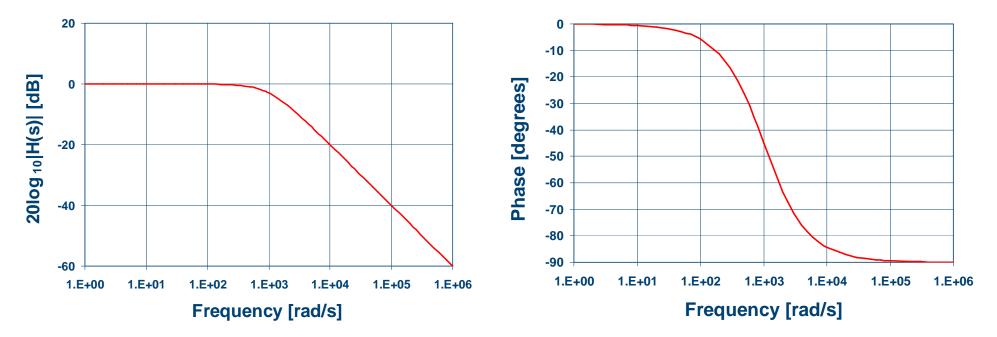

Many interesting properties of the frequency behavior of a given circuit can be obtained plotting the module and the phase of the Transfer Function as a function of the frequency. These plots are called Bode diagrams. In the general case, a transfer function is given by the ratio between two polynomials. The roots of the numerator polynomial are called zeros, the roots of the denominator polynomials are called poles. For example, in the case of a low-pass filter with RC = 1 ms, the Bode diagrams look like:

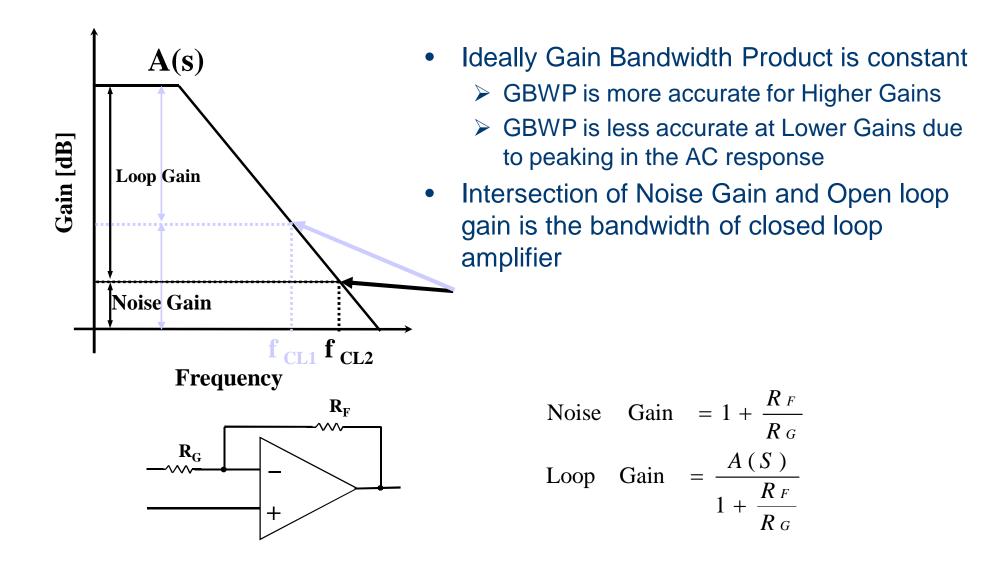

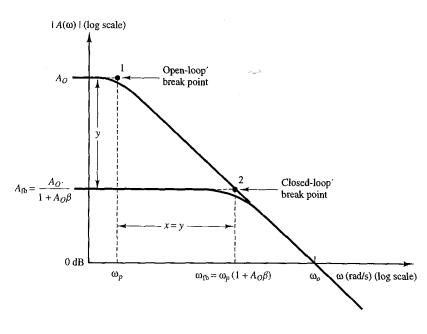

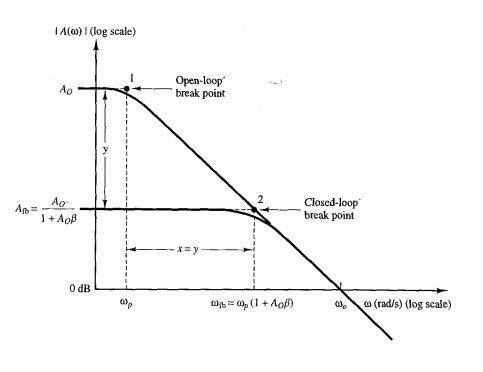

### Bandwidth increase with feedback

The gain-bandwidth product does not change with feedback!

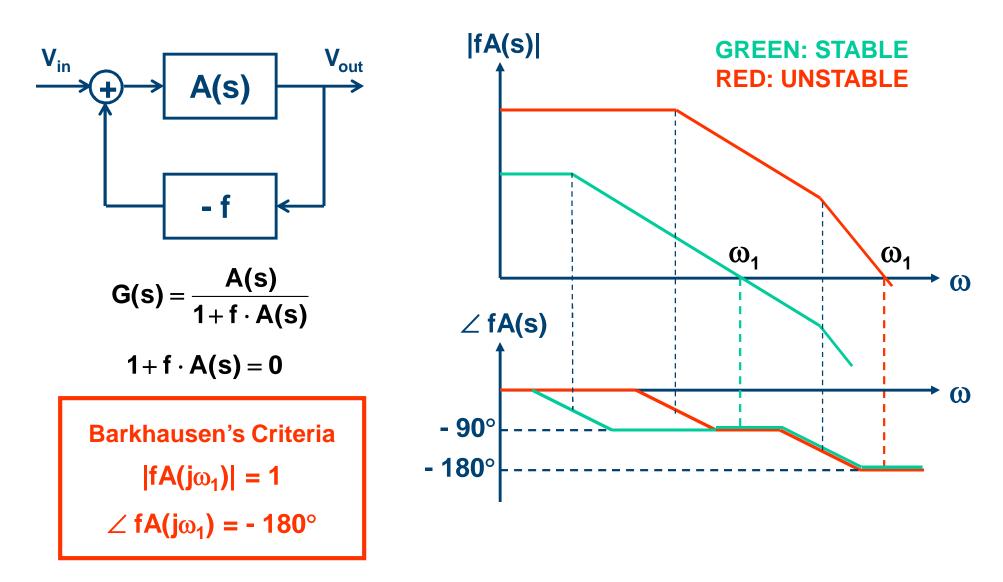

# **Stability Criteria**

31

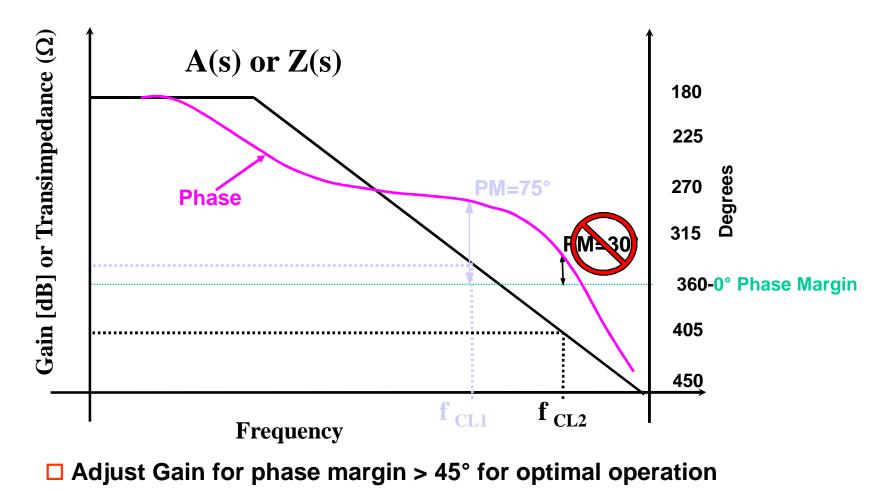

### Phase Margin

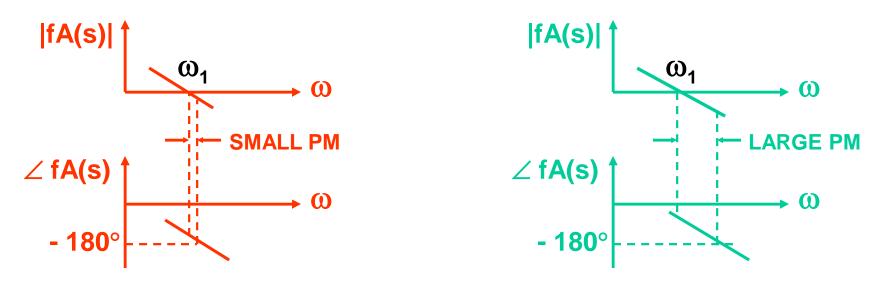

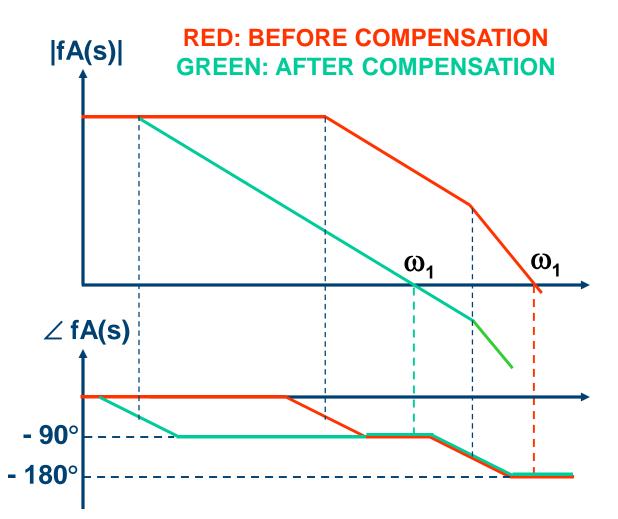

We have seen that to ensure stability |fA(s)| must be smaller than 1 before  $\angle fA(s)$  reaches - 180°. But, in fact, to avoid oscillation and ringing, we must have a bit more margin.

We define phase margin (PM) the quantity  $180^{\circ} + \angle fA(\omega_1)$ , where  $\omega_1$  is the gain crossover frequency. It can be shown that, to have a stable system with no ringing (for small signals) we must have PM > 60°. If we want to have an amplifier which responds to a large input step without ringing, PM must be even higher.

### **Frequency Compensation**

Single-pole op-amps would always be stable (the phase does not go below - 90°). But a typical op-amp circuit always contains several poles (and zeros!). These opamps can easily be unstable, and they need therefore to be compensated. This is generally done lowering the frequency of the dominant pole.

# Outline – Part II

- Noise in analog ICs

- Matching in analog ICs

- Operational Amplifier design examples

- Analog design methodology

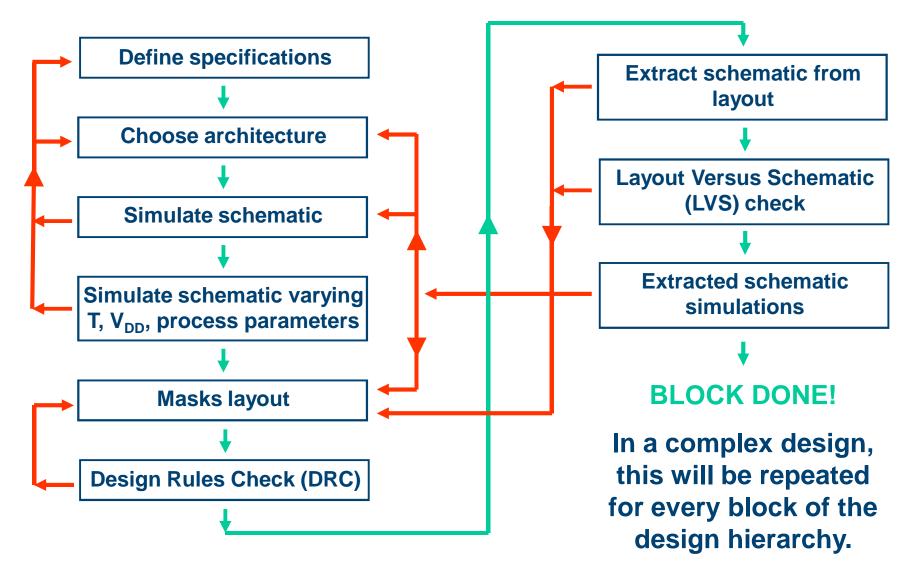

### Analog design methodology

## **Unit II: HIGH FREQUENCY AND NOISE OF CHARACTERISTICS AMPLIFIERS**

## **Presentation Agenda**

- High-Speed Amplifiers

- Voltage Feedback vs. Current Feedback

- Differential Amplifiers

- Precision Amplifiers

- AutoZero

- Digitrim

- Instrumentation and Industrial

- High CMRR

- ≻ VGA

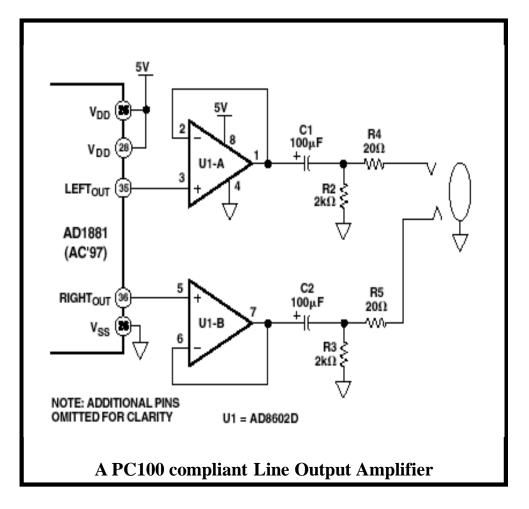

## **High-Speed Amplifiers**

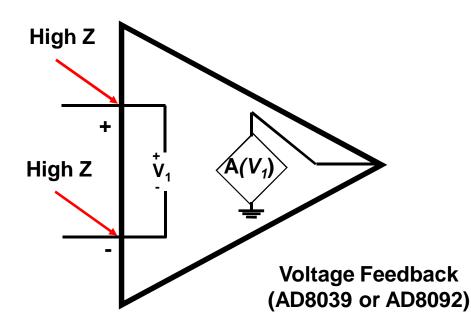

### Voltage Feedback vs. Current Feedback Simplified Architecture Relationship Between Feedback and Bandwidth Stability

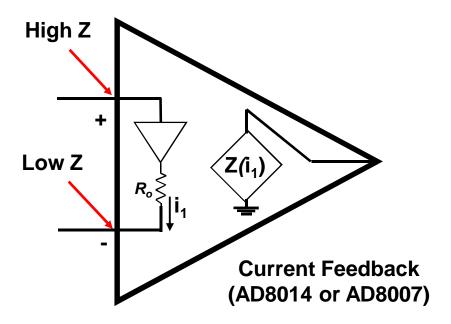

## Simplified Block Diagrams

Voltage Feedback vs. Current Feedback

- Error Voltage (V<sub>1</sub>) Amplified by the Open loop Gain (A)

- Closed Loop forces Error Voltage to be zero

- Error Current (i<sub>1</sub>) Amplified by the Transimpedance Gain (Z)

- Closed Loop forces the Error Current to be zero making the Input Voltages equal

## Voltage Feedback Frequency Response

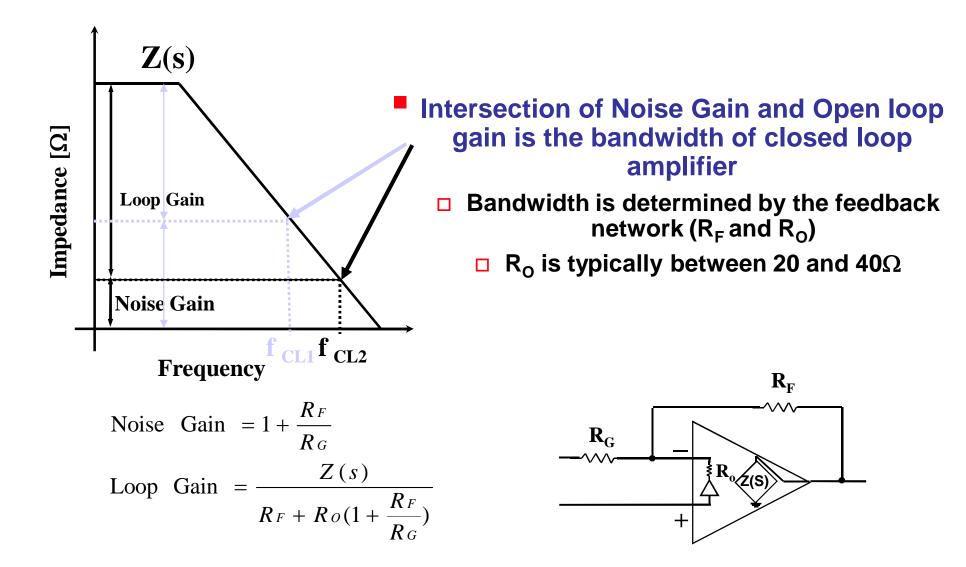

## Current Feedback Frequency Response

## **Stability Analysis**

#### Same for Voltage and Current Feedback

□< 30° is unsafe

## **Differential Amplifiers**

Benefits of Differential Amplifiers

Architectures of Differential Amplifiers

Applications of Differential Amplifiers

## Primary Uses for Differential Amps

- Differential Signal Processing

- Avoid Ground Noise

- High Dynamic Range on Low Supplies

- Differential Filters

- High Speed ADC Driving

- > All High Speed ADC Perform Better when Driven Differentially

- Amplify and Buffer DAC outputs

- Differential Amplifiers Reduce Clock Jitter

- Twisted-pair Line Driving/Receiving

- Simplifies circuit design

- Balanced Outputs Minimize EMI

- High CMRR Reduces EMI Susceptibility

## Benefits of Differential Signal Processing

- Maximize Speed and Resolution with Differential Amps

- > Avoid Grounding/Return Noise Problems

- Analog Signals in High-performance Systems Start and End Differential

- Almost Always the Signal Source from the Real World is Differential

- High-speed ADCs Have Differential Inputs

- Better Distortion/Dynamic Range than Single-Ended Op-Amps

- More Output Headroom for the same Signal Amplitude

- Or Lower Distortion for the same output swing especially the 2nds

## High Speed Differential Amps for Challenging Designs

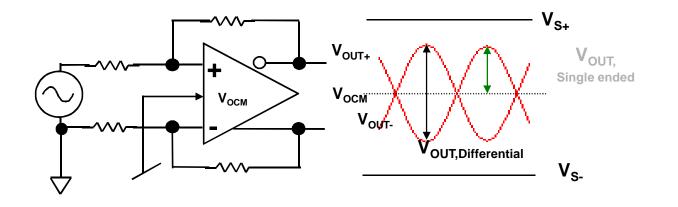

3 Main Signal Characteristics of Differential Signals

Equal in amplitude, and opposite in phase

Differential Amplitude = 2x either Single Ended output

Centered at common voltage, V<sub>OCM</sub>

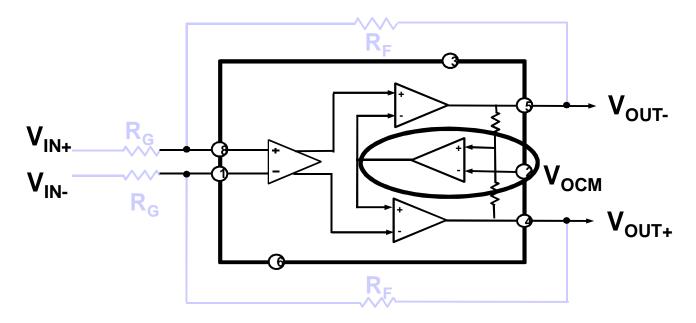

## What's Inside the Analog Devices Differential Amplifiers?

#### Internal CM Feedback forces Forces both outputs to be balanced

**Equal in amplitude 180° out of phase:**  $V_{OUT, CM} = (V_{OUT+} + V_{OUT-})/2)$

Balance is unaffected by R<sub>F</sub>/R<sub>G</sub> matching

- Differential feedback effectively creates 2 summing nodes

- Forces Both Inputs to the same voltage when the loop is closed

**High Input Z, Low Output Z**

## More About the V<sub>OCM</sub> Pin

### • V<sub>OCM</sub> Pin

- Creates Best Available Balance @ High Frequencies

- By Forcing Outputs to be equal

- ➢ For AC signals and DC Reference Voltages

- For Easy Level Shifting

- From Ground Referenced Signals (+/-5V supplies) to Single +5V Supply Signals

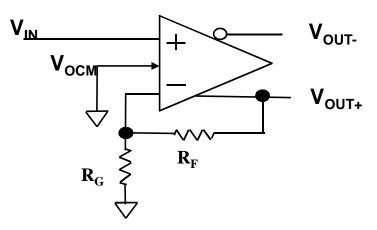

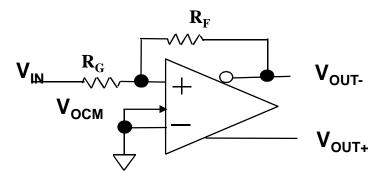

## Understanding How They Work w/ Alternate Circuit Configurations

#### Like Non-inverting Op Amp

Like Inverting Op Amp

2 Feedback Loops

- Differential feedback forces inputs to the same voltage

- Common mode Feedback forces V<sub>OUT-</sub> = -V<sub>OUT+-</sub>

- Non-inverting example:

For R<sub>F</sub> = 0

V<sub>Out+</sub> = V<sub>IN</sub>

Gain = 2

Inverting example:

For R<sub>F</sub> = R<sub>G</sub>

High input Z summing node

$V_{out-} = -V_{IN}$ Gain = 2

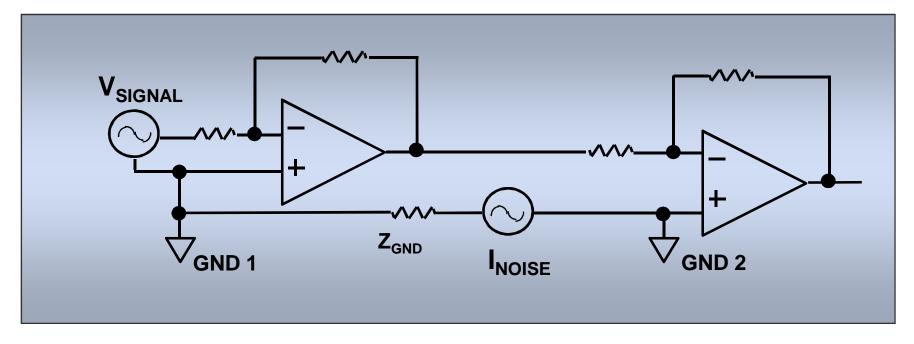

## Single-ended Components Cannot Reject Ground Noise

- Each Part of the Circuit Has a Different Reference Point

- High Frequency Ground Currents will Cause Problems

- Op Amp Can not Reject This Ground Noise

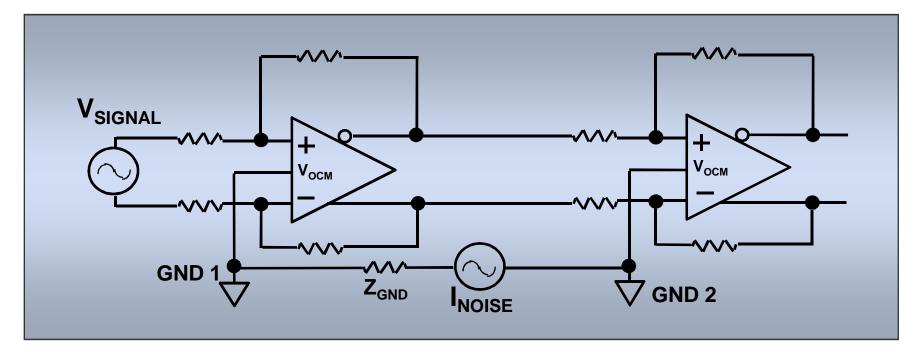

## Differential Amps Have Effective CMRR

- Differential Signal does not Need a Reference

- Ground and Other Noise Sources are Common to Both Inputs

- CMRR of Differential Amp is Effective

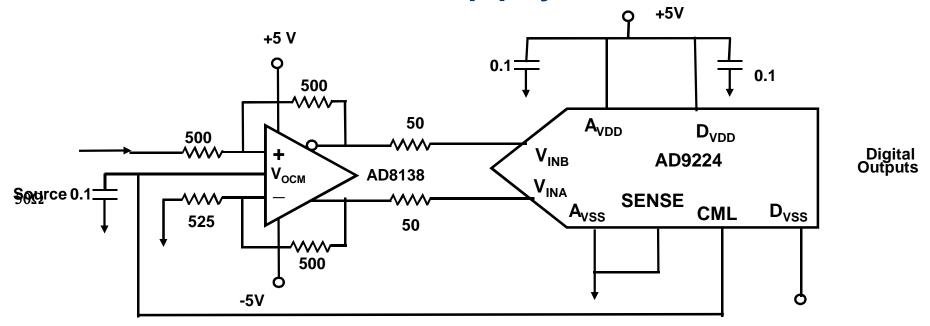

## Driving High-Performance ADC on 5V Supply

ADC Reference CML output drives V<sub>OCM</sub> to set optimum CM output

Easy level shift using V<sub>OCM</sub>

Better Distortion in signal chain for +/-5V, than +5V

**Connect to the ADC reference or any other reference voltage**

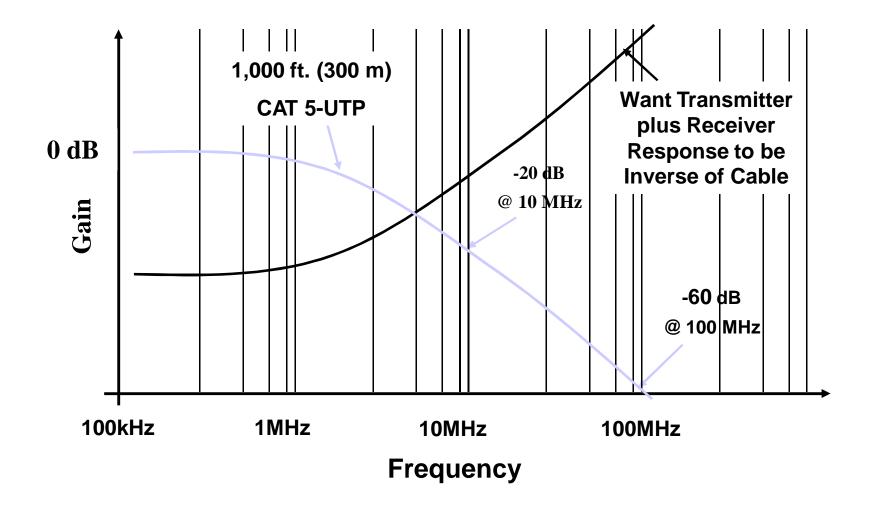

## Cable Driving Challenge

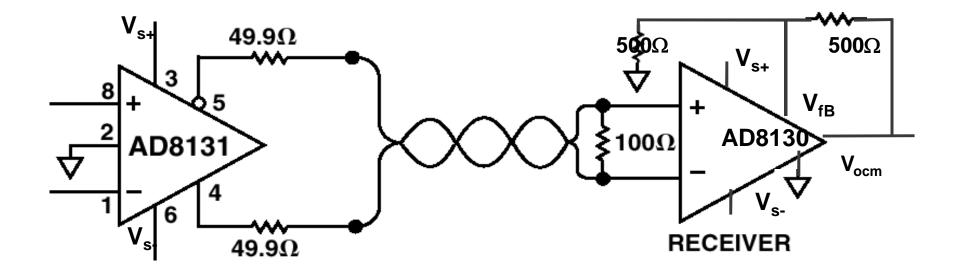

## **Differential Driver and Receiver**

- Balanced Driver Minimizes EMI Generation

- High CMRR Receiver Minimizes EMI Pick-up

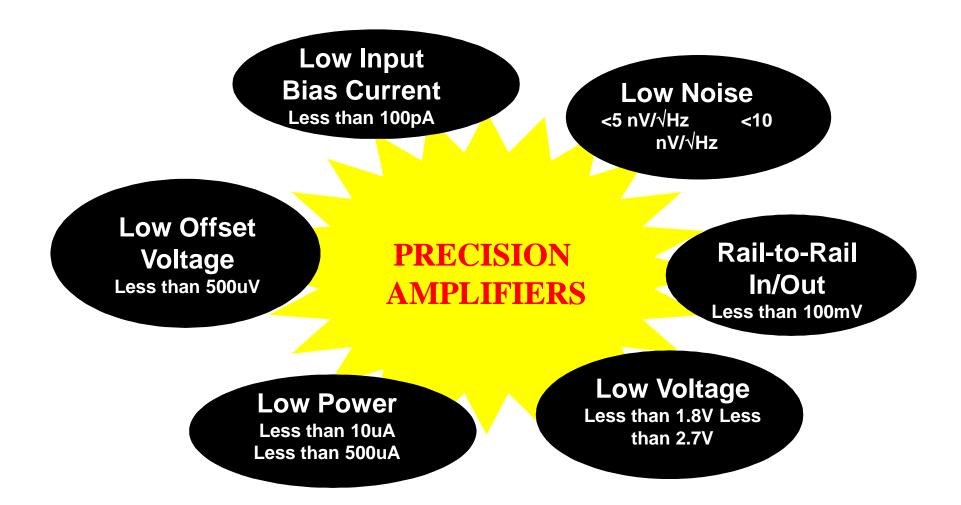

## **Precision Amplifiers**

# Precision Amplifier Segments...

**Amplifier Characteristics Define Market**

####

## AD855x,AD857x families &

- $1\mu V$  of typical offset voltage ( $5\mu V$  max.)

- 5 nV/°C of TCV<sub>OS</sub> from -40°C to +85°C

> That's less than 600 nV of drift over the entire temp. range

- CMRR and PSRR are offset voltages due to changes in  $V_{\text{CM}}$  and  $V_{\text{SY}}$

CMRR and PSRR are >135dB (or <0.3ppm)</p>

• 1/f noise, which increases at 3dB per octave decrease, can also be viewed as an offset error

> The AD855x, AD857x and AD8628 exhibit NO 1/f noise!

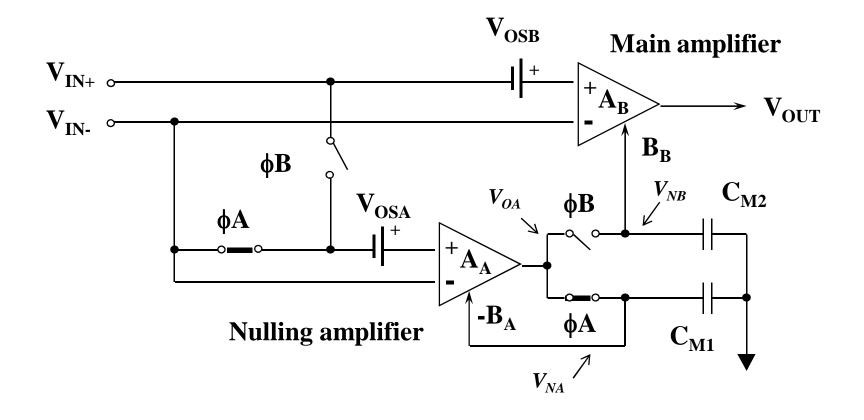

## Simplified Schematic of AD855x

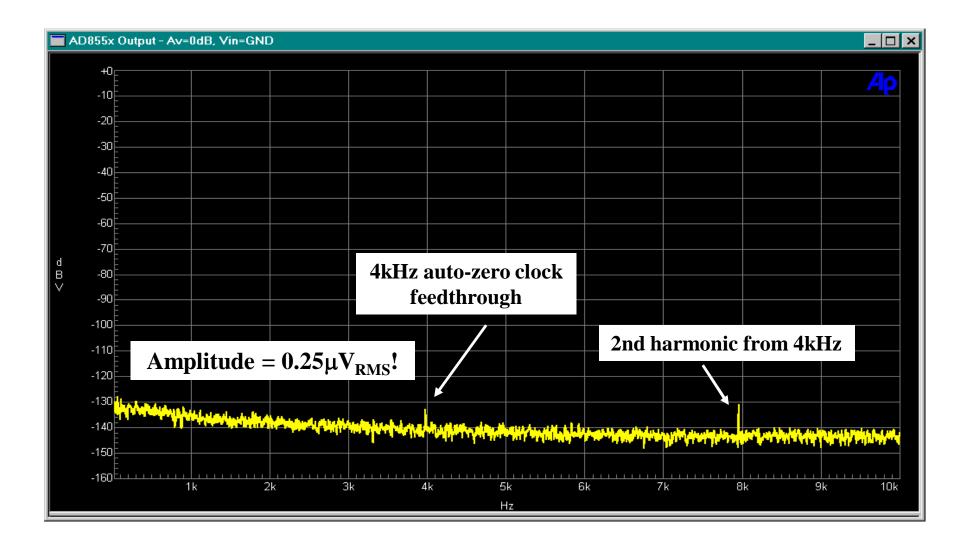

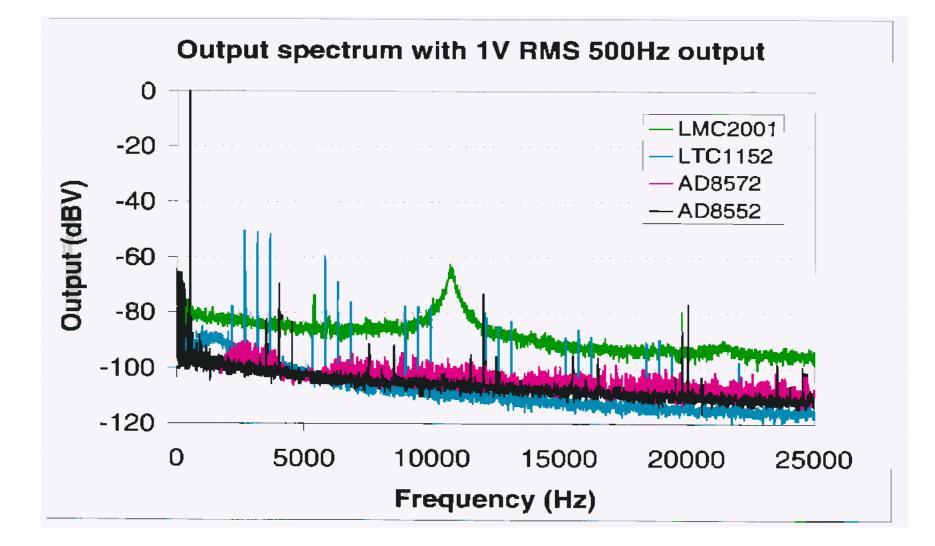

# Spectral analysis of AD855x output in unity gain

## **IMD+Noise Comparison**

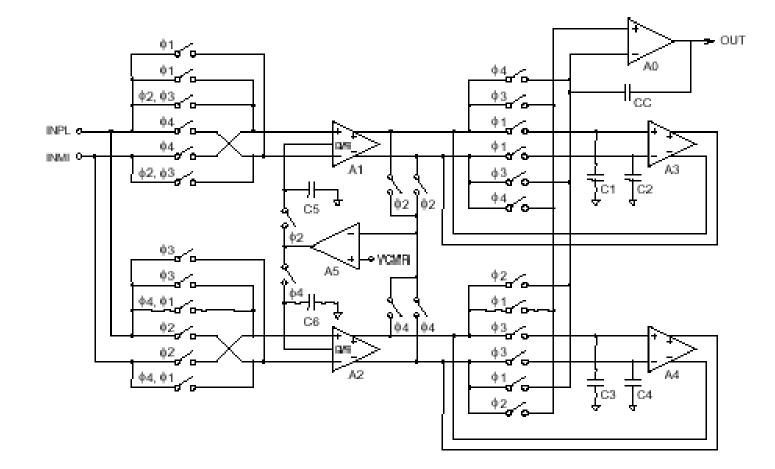

# 2nd Generation Auto-zero amp

- SOT-23 package !!!

- Best noise ever for auto-zero--20nV/√Hz

> Like non-auto-zero amplifiers

- Low Clock noise

- 2.2MHz Gain-Bandwidth

- No Compromise in auto-zero DC precision

- 16 bits absolute accuracy: 0-10kHz—including noise

Photodiodes, Portable scales, current sensors, IR sensors, strain bi sensors

World's Highest Precision Amplifier

Release in April 2002 mote

Ú

## "Simplified" diagram of AD8628 amplifier

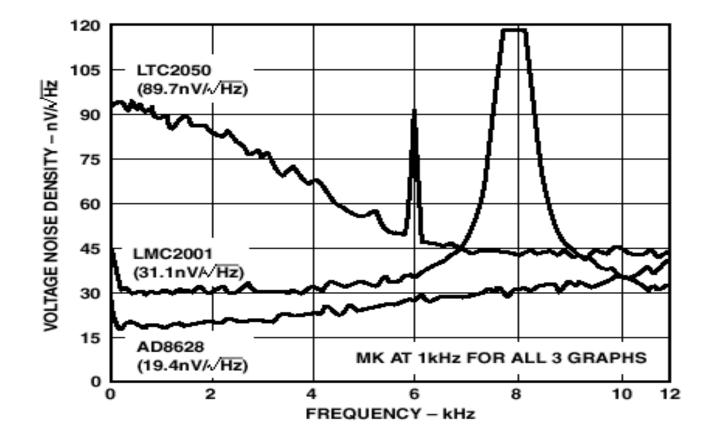

## AD8628 Noise Spectral Density Comparison

## **Precision Amplifiers**

# **DigiTrim Amplifiers**

- Digitrim is a proprietary technology used to digitally adjust an in-package IC without adding any extra digital input pins

- On the AD8601/2/4 family, DigiTrim adjusts offset voltage to  ${<}500\mu V$

- On the AD8603/7/9 family, DigiTrim adjusts offset voltage to  ${<}100\mu V$

- On the AD8605/6/8 family, DigiTrim adjusts offset voltage to  ${<}65\mu V$

## Advantages of DigiTrim<sup>®</sup>

- In-package trim

- Mechanical stress on the die causes  $V_{OS}$  errors

- This can ruin any wafer trimming already done

- Lots of stress on SOT23 and SC70 packages

- By trimming in-package you trim out post-stress V<sub>OS</sub>!

- No special processing Foundry OK

- As processing shrinks, trim area is smaller too

- No extra pads required

- Higher test throughput

All this adds up to LOWER COST

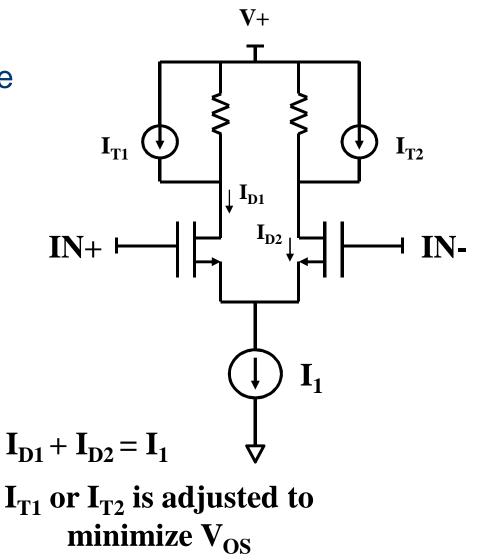

# How is $V_{OS}$ trimmed?

- Extra current is put into one side (or the other) of the input diff pair

- This current difference creates an offset voltage between the diff pair transistors

## Some Trim Comparisons

|           | Trimmed<br>at: | Special<br>Processing | Resolution |

|-----------|----------------|-----------------------|------------|

| Laser     | Wafer          | Thin Film             | Continuous |

| Zener Zap | Wafer          | None                  | Discrete   |

| Link      | Wafer          | TFR or Poly           | Discrete   |

| EEPROM    | Wafer or FT    | EEPROM                | Discrete   |

| Chopper   | N/A            | CMOS                  | Continuous |

| DigiTrim  | Wafer or FT    | None                  | Discrete   |

## AD8601/2/4 DigiTrim<sup>®</sup> Amplifiers

- V<sub>OS</sub> < 500μV

- Bandwidth 8MHz

- Input Bias Current <60pA max. (<1pA typ)</li>

- $\Box \quad \Delta V_{OS} / \Delta T 2\mu V /^{\circ} C \text{ typ}$

- Supply Current 840µA/amplifier

- SOT23 package (single)

# Next Generation DigiTrim<sup>®</sup>

- AD8605/6/8 Low noise DigiTrim ®

- ➤ Low noise—8nV/√Hz

- Low offset--65µV max!

- Very low input bias current– 1pA max!

- Fast--10MHz bandwidth

- High CMRR, PSRR and Gain

- Single in SOT23 and Wafer Level Chip-scale!

- AD8603/7/9 Low power/low noise DigiTrim ®

- Low Power--60µA per amplifier

- Low offset--<100µV max</p>

- ≻ Low noise--30nV/√Hz

- 350kHz bandwidth

- 1.8V to 5V operation

Release in April

Low Noise

**CMOS**

## High Precision Low Power

Photodiodes, Portable scales, current sensors, strain bridges (pressure), remote sensors

# Top Core Applications

#### • Photo-diode amp

- Thermal sensing

- Infrared

- > Thermocouples

- > RTD

- Current sensing

- Motor controls

- Laser Diode Power Controls

- Battery Controls

- Strain Bridges

- Level setting and detecting

- Integrator

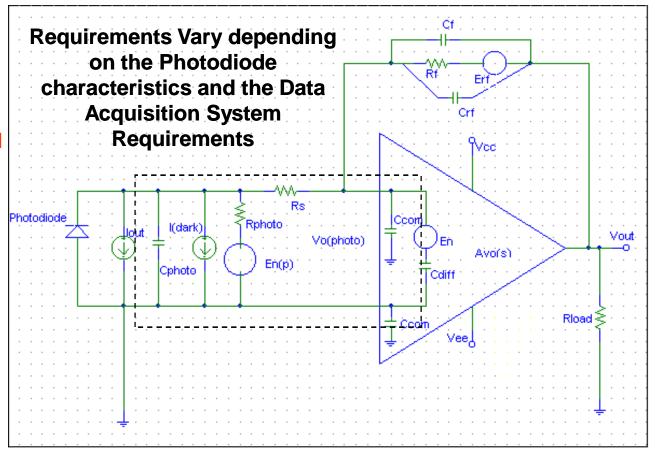

## trans-impedance amplifier

Key Requirements Low input bias current Low Offset Voltage Low Drift Low Cin Bandwidth (Varies) Wide Dynamic Range

#### **Key Parts**

CMOS AD855X AD857X AD8601/2/4 AD8605/6/8 AD8628 AD8651

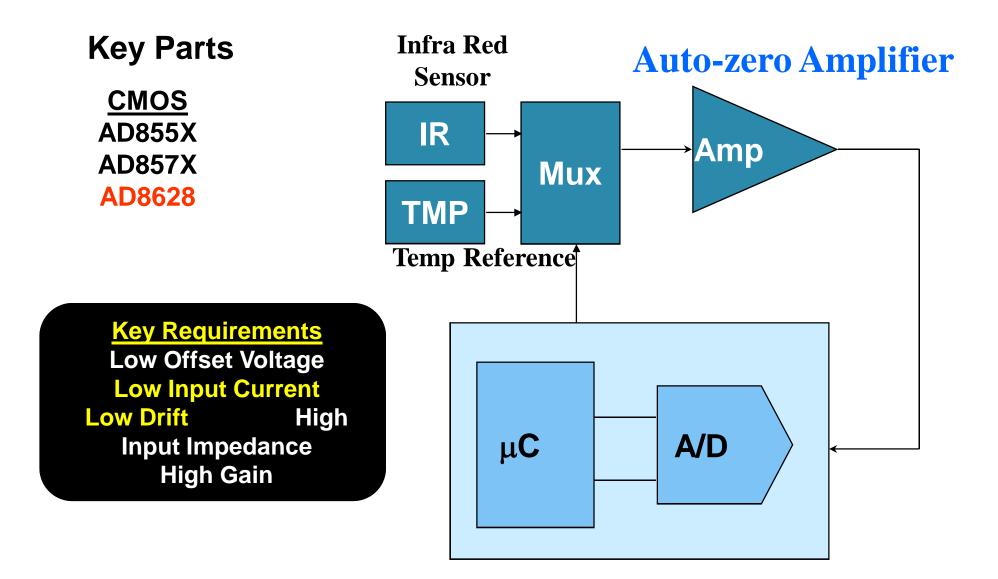

## **IR Thermal Sensing**

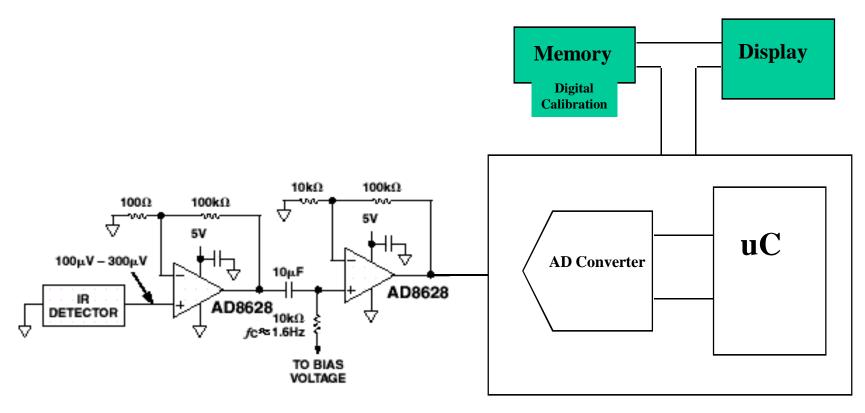

## Typical implementation (IR Thermal Sensing)

#### **Micro-Controller**

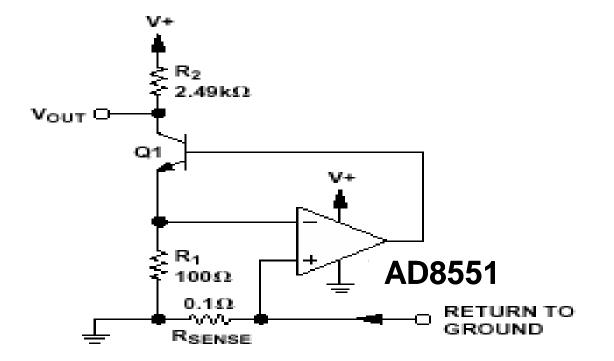

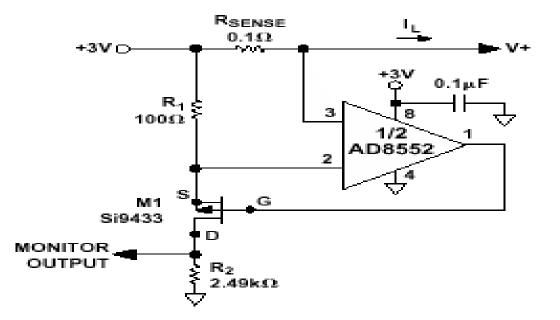

#### Low Side sensing with I sink

V(out) = (V+)-(R2/R1 \* Rsense \* IL)

**Features: Allows Sinking of current**

#### High Side Sensing with current sink

#### Monitor Output = R2 \*(Rsense /R1) \* IL

Features : Great CMRR, very Low Vos , Allows Sinking of Current

#### Analysis of Low Side sensing circuit

| Parameter    | AD8565      | AD8551     | OP777        |

|--------------|-------------|------------|--------------|

| Vcc Range    | 4.5V to 16V | 2.7V to 5V | 2.7V to 30V  |

| Rail To Rail | I/O         | I/O        | -Rail only/O |

| Vos          | 10mV        | 5μV        | 100µV        |

| TcVos        | 5μV/C       | 10nV/C     | 1.3μV/C      |

| IB           | 600nA       | 50pA       | 11nA         |

| CMRR         | 54dB        | 110dB      | 110dB        |

| lsy          | 850µA       | 600µA      | 230µA        |

## Minimum measured I<sub>Return</sub> based on Amplifier Errors

|                           | AD8565 | AD8551 | OP777 |

|---------------------------|--------|--------|-------|

| Vos<br>contribution       | 100mA  | 50μΑ   | 1mA   |

| TcVos<br>contribution     | 5mA    | 40µA   | 1.3mA |

| Bias Current contribution | 600μΑ  | 40nA   | 11µA  |

| Min I <sub>Return</sub>   | 110mA  | 100µA  | 2.5mA |

#### Instrumentation and Industrial

Instrumentation AmplifiersVariable Gain Amplifiers

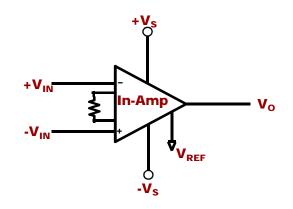

## What is an Instrumentation Amplifier

- It has many applications beyond instrumentation

- Under the category of instrumentation amplifier, there are also: difference amplifier, HCMV amplifier, and differential-to-single ended amplifier

- It could also be thought of as an IC with multiple op amps and laser trimmed resistors

#### What Does an Instrumentation Amplifier

- Measures small precision signals in oisy environments

- Rejects common mode voltage (noise)

**Differential Input**

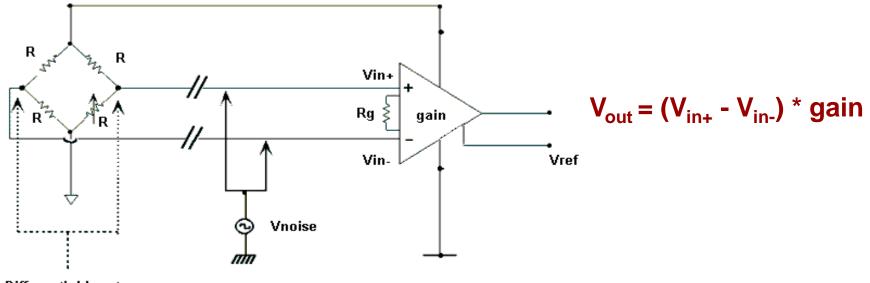

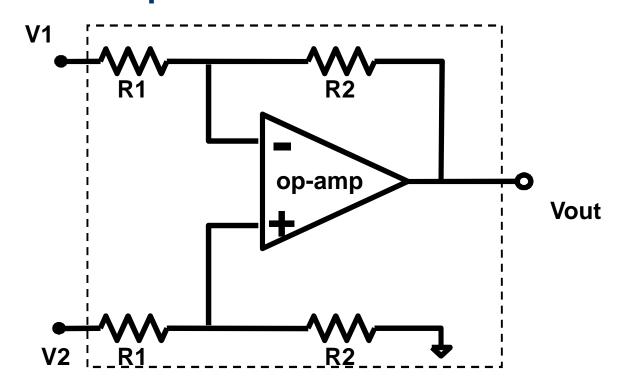

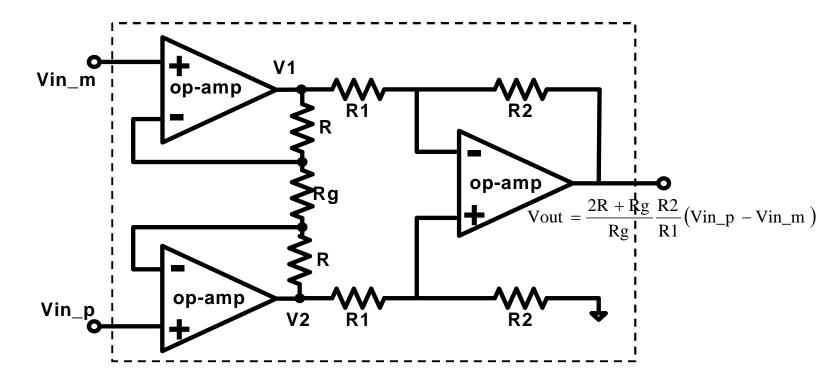

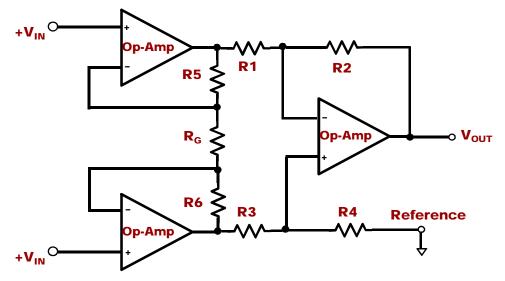

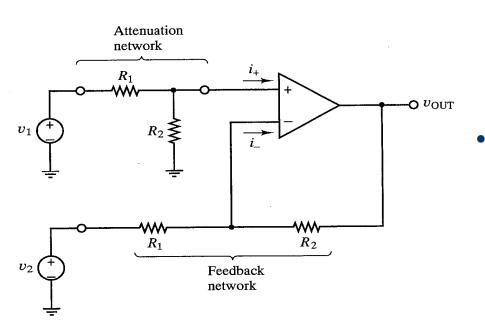

#### Understanding the Difference Amplifier Architecture

- When R1=R2

- When R1≠ R2

Vout = V2-V1 Vout = (V2-V1)\*R2/R1

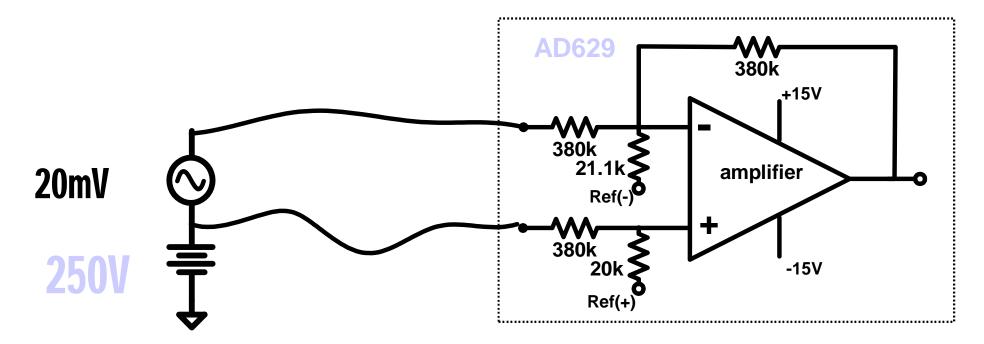

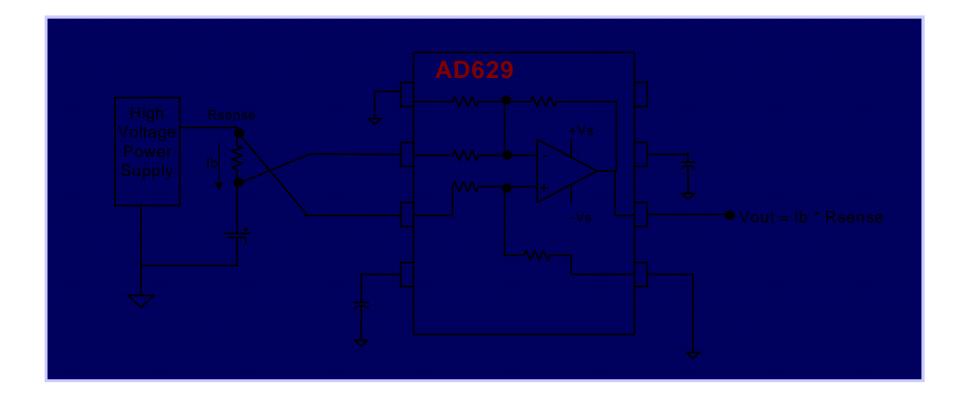

## Difference Amplifiers Have High Common Mode Voltage Range

- With Difference Amplifiers, the input voltage can be higher than the supply voltage.

- This Difference Amplifier operates on +/-15V, gains the 20mV signal and rejects the +/-250V common-mode signal.

## Difference Amplifier Application for Battery Charger

+/-500V Input Voltage Protection

#### Understanding the Instrumentation Amplifier Architecture

•Difference Amplifier •Buffered Inputs

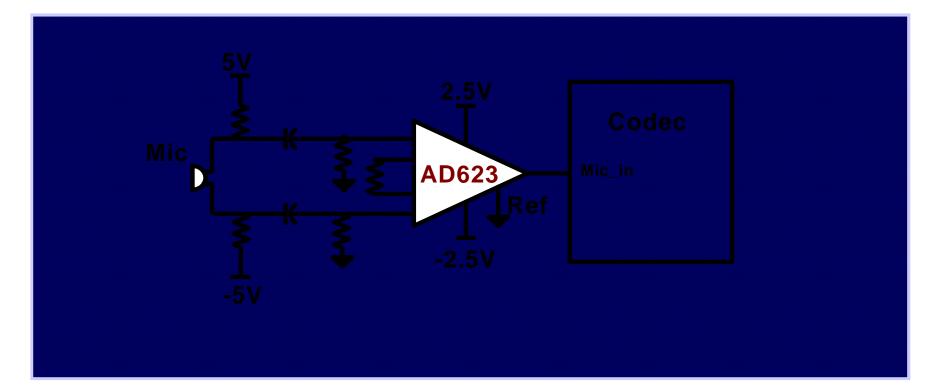

# Instrumentation Amplifier Application for PDA

• Instrumentation Amplifier removes 60Hz noise from the body and surroundings to provide a clear signal into the Codec.

#### Monolithic vs. Discrete Designs for Instrumentation Amplifiers Discrete Monolithic

•3 op amps

•7-9 resistors

•More board space

•Higher cost

•250% more error than monolithic solutions

1 instrumentation amplifier

1 resistor

Less board space

Lower cost

Better performance

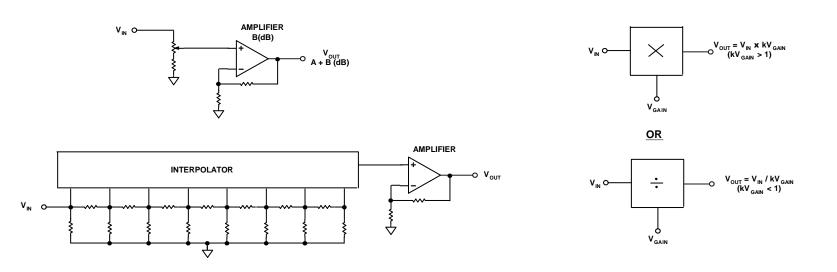

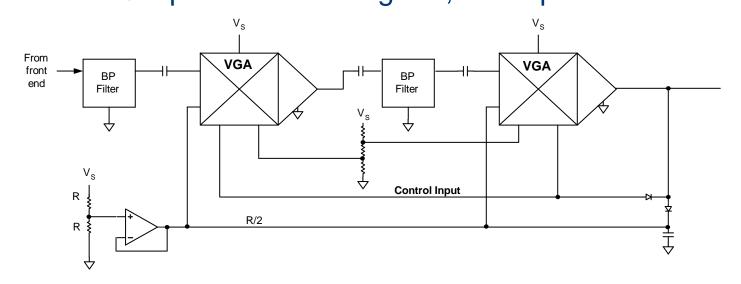

#### What is a Variable Gain Amplifier

- A variable gain amplifier is a special kind of amplifier whose gain can be dynamically controlled in 'real-time' by an externally applied control voltage. In its simplest form, it can be visualized as an amplifier with an electronic gain control.

- Analog Devices makes variable gain amplifiers that cover frequencies ranging up to 1GHz. The variable gain amplifiers covered in this presentation are the low speed ones <250MHz</li>

#### How do Variable Gain Amplifiers Work?

Analog Devices builds two basic styles of VGAs, the X-Amp and the translinear core (aka analog multiplier.) X-Amps are complex and expensive to manufacture but have low noise. Translinear cores are simpler structures and thus lower cost, but more noisy. The block diagrams of the two styles are shown below:

X-Amp

**Translinear Core**

The X-amp (exponential) uses a resistor ladder as the gain element. An array of special amplifiers (interpolator)steer current among the taps.

Translinear cores can be configured as a multiplier or divider. A VGA can operate in either mode.

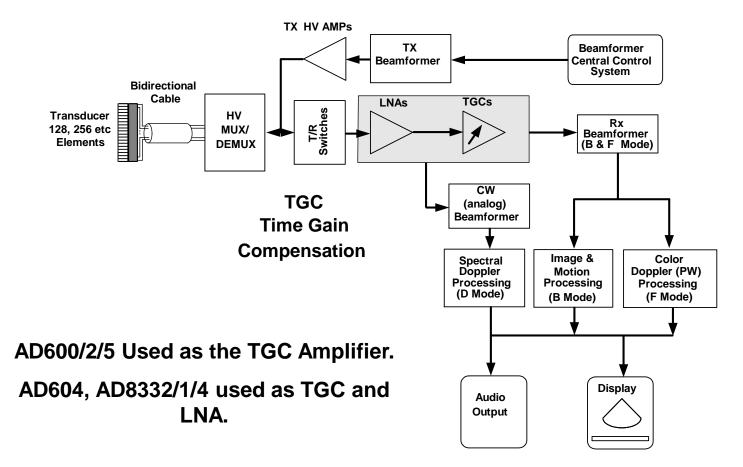

#### When Do You Use a VGA?

- In certain applications, the information of interest is contained within a widely-changing dynamic signal. Examples of these kinds of signals are an returning ultrasound echo and a communications signal (Intermediate Frequency) in a receiver. An amplifier with fixed gain (including a PGA,) will operate linearly (i.e. without distortion or saturation) for low-level <u>or</u> high-level signals, but **not** both.

- A VGA provides a means of amplifying such signals, without distortion or saturation, and can be used as the controlled element of an Automatic Gain Control (AGC) circuit in a receiver, or as the controlling amplifier in a Timed-Gain-Control circuit of an Ultrasound system.

#### VGAs Used in an Ultrasound System

#### VGAs Used in Communications Systems • Simplified Block Diagram, IF Amplifier

Typical IF Frequency is 10.7 MHz, however our VGAs have also been used at 455 kHz, 44MHz, and higher (at the users peril.) The AD8330 should be ideal for such circuits thanks to low cost and good high-frequency performance.

#### <u>Unit - III</u>

#### **FEEDBACK AND OPERATIONAL AMPLIFIERS**

## **Operational Amplifiers**

- An operational amplifier (called op-amp) is a specially-designed amplifier in bipolar or CMOS (or BiCMOS) with the following typical characteristics:

- Very high gain (10,000 to 1,000,000)

- Differential input

- Very high (assumed infinite) input impedance

- Single ended output

- Very low output impedance

- > Linear behavior (within the range of  $V_{NEG} < v_{out} < V_{POS}$

- Op-amps are used as generic "black box" building blocks in much analog electronic design

- > Amplification

- Analog filtering

- Buffering

- Threshold detection

- Chapter 2 treats the op-amp as a black box; Chapters 8-12 cover details of op- amp design

- > Do not really need to know all the details of the op-amp circuitry in order to use it

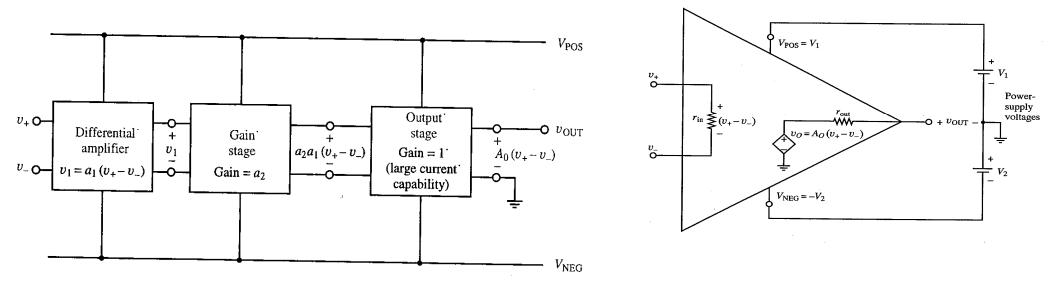

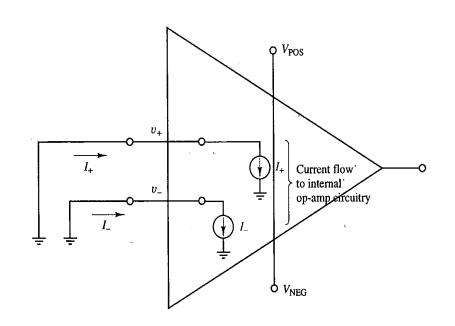

#### **Generic View of Op-amp Internal Structure**

- An op-amp is usually comprised of at least three different amplifier stages (see figure)

- > Differential amplifier input stage with gain  $a_1(v_1 v_2)$  having inverting & non-inverting inputs

- > Stage 2 is a "Gain" stage with gain  $a_2$  and differential or singled ended input and output

- Output stage is an emitter follower (or source follower) stage with a gain = ~1 and singleended output with a large current driving capability

- Simple Op-Amp Model (lower right figure):

- $\succ$  Two supplies V<sub>POS</sub> and V<sub>NEG</sub> are utilized and always assumed (even if not explicitly shown)

- An input resistance r<sub>in</sub> (very high)

- An output resistance r<sub>out</sub> (very low) in series with output voltage source v<sub>o</sub>

- > Linear Transfer function is  $v_0 = a_1 a_2(v_1 v_2) = A_0(v_1 v_2)$  where  $A_0$  is open-loop gain

- ▶  $v_o$  is clamped at  $V_{POS}$  or  $V_{NEG}$  if  $A_o (v_+ v_-) > V_{POS}$  or  $< V_{NEG}$ , respectively

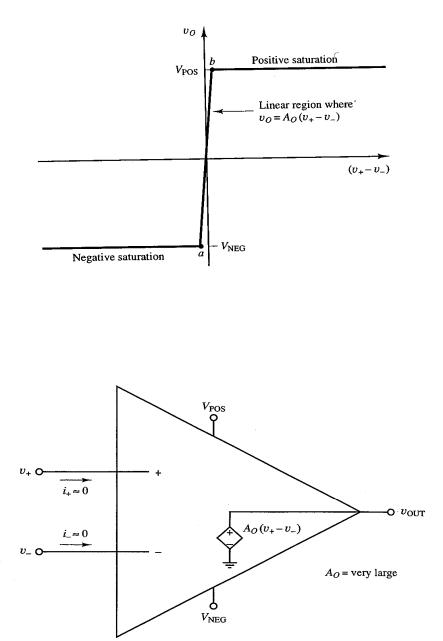

#### **Ideal Op-amp Approximation**

- Because of the extremely high voltage gain, high input resistance, and low output resistance of an op-amp, we use the following ideal assumptions:

- > The saturation limits of  $v_0$  are equal  $V_{POS} \& V_{NEG}$

- If (v<sub>+</sub> v<sub>-</sub>) is slightly positive, v<sub>0</sub> saturates at V<sub>POS</sub>; if (v<sub>+</sub> - v<sub>-</sub>) is slightly negative, v<sub>0</sub> saturates at V<sub>NEG</sub>

- If v<sub>0</sub> is not forced into saturation, then (v<sub>+</sub> v<sub>-</sub>) must be very near zero and the op-amp is in its linear region (which is usually the case for negative feedback use)

- The input resistance can be considered infinite allowing the assumption of zero input currents

- The output resistance can be considered to be zero, which allows V<sub>out</sub> to equal the internal voltage V<sub>0</sub>

- The idealized circuit model of an op-amp is shown at the left-bottom figure

- The transfer characteristic is shown at the left-top

- Op-amps are typically used in negative feedback configurations, where some portion of the output is brought back to the negative input v.

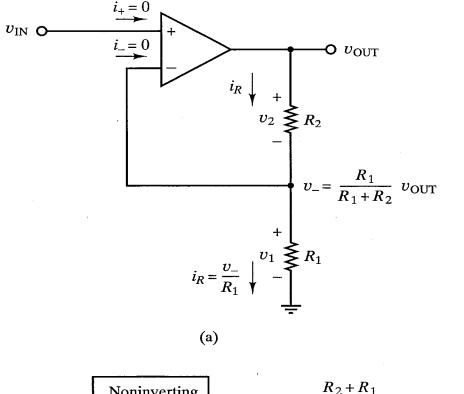

#### Linear Op-amp Operation: Non-Inverting Use

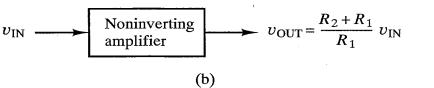

Fig. 2.5 (a) Noninverting amplifier configuration; (b) block diagram of circuit's operational function.

- Shown at left is an ideal op-amp in a noninverting configuration with negative feedback provided by voltage divider R1, R2

- Determination of closed-loop gain:

- Since the input current is assumed zero, we can write v = R1/(R1 + R2)v<sub>OUT</sub>

- But, since v<sub>+</sub> =~ v<sub>-</sub> for the opamp operation in its linear region, we can write

$v_{-} = v_{IN} = R1/(R1 + R2)v_{OUT}$

or, **v<sub>out</sub> = ((R1 + R2)/R1)v<sub>IN</sub>**

MICROELECTRONIC CIRCUITS AND DEVICES Second Edition by Horenstein © 1996 by Prentice-Hall, Inc. A Simon & Schuster Company Englewood Cliffs, NJ 07632 We can derive the same expression by writing

$v_{OUT} = A(v_+ - v_-) = A\{v_{IN} - [R1/(R1 + R2)]v_{OUT}\}$ and solving for  $v_{OUT}$  with A>>1 Look at Example 2.1 and plot transfer curve.

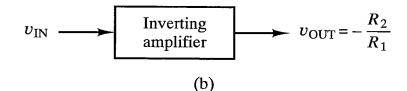

#### The Concept of the Virtual Short

- The op-amp with negative feedback forces the two inputs v+ and v- to have the same voltage, even though no current flows into either input.

- > This is sometimes called a "virtual short"

- As long as the op-amp stays in its linear region, the output will change up or down until v- is almost equal to v+

- ▶ If  $v_{IN}$  is raised,  $v_{OUT}$  will increase just enough so that  $v_{-}$  (tapped from the voltage divider) increases to be equal to  $v_{+}$  (=  $v_{IN}$ )

- In  $v_{IN}$  is lowered,  $v_{OUT}$  lowers just enough to make v- = v+

- > The negative feedback forces the "virtual short" condition to occur

- Look at Exercise 2.4 and 2.5

- For consideration:

- What would the op-amp do if the feedback connection were connected to the v+ input and v<sub>IN</sub> were connected to the v- input?

- Hint: This connection is a positive feedback connection!

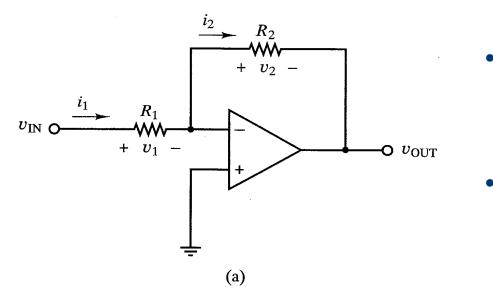

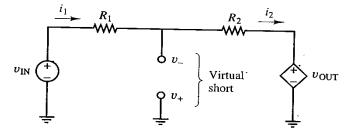

#### Linear Op-amp Operation: Inverting Configuration

Fig. 2.8 (a) Inverting amplifier configuration; (b) block diagram of circuit's operational function.

MICROELECTRONIC CIRCUITS AND DEVICES Second Edition by Horenstein

© 1996 by Prentice-Hall, Inc. A Simon & Schuster Company Englewood Cliffs, NJ 07632

- An op-amp in the inverting configuration (with negative feedback) is shown at the left

- Feedback is from v<sub>OUT</sub> to v- through resistor R2

- $\succ$  v<sub>IN</sub> comes in to the v- terminal via resistor R1

- v+ is connected to ground

- Since  $v_{-} = v_{+} = 0$  and the input current is zero, we can write

- The circuit can be thought of as a resistor divider with a virtual short (as shown below)

- If the input v<sub>IN</sub> rises, the output v<sub>OUT</sub> will fall just enough to hold v- at the potential of v+ (=0)

- If the input v<sub>IN</sub> drops, v<sub>OUT</sub> will rise just enough to force v- to be very near 0

- Look at Example 2.2 and Exercises 2.7-2.10

#### Input Resistance for Inverting and Non-inverting Op-amps

- The non-inverting op-amp configuration of slide 2-4 has an apparent input resistance of infinity, since i<sub>IN</sub> = 0 and R<sub>IN</sub> = v<sub>IN</sub>/i<sub>IN</sub> = v<sub>IN</sub>/0 = infinity

- The inverting op-amp configuration, however, has an apparent input resistance of R1

- > since  $R_{IN} = v_{IN}/i_{IN} = v_{IN}/[(v_{IN} 0)/R1] = R1$

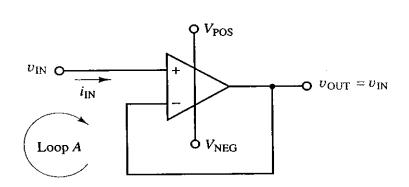

#### **Op-amp Voltage Follower Configuration**

- The op-amp configuration shown at left is a voltage-follower often used as a buffer amplifier

- Output is connected directly to negative input (negative feedback)

- Since v+ = v- = v<sub>IN</sub>, and v<sub>OUT</sub> = v-, we can see by inspection that the closed-loop gain A<sub>o</sub> = 1

- We can obtain the same result by writing

$$v_{OUT} = A (v_{IN} - v_{OUT})$$

or

**v**<sub>OUT</sub>/**v**<sub>IN</sub> = A/(1 + A) = 1 for A >> 1

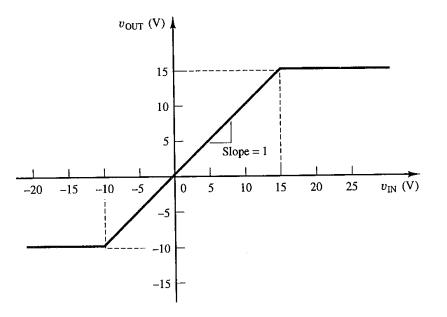

- A typical voltage-follower transfer curve is shown in the left-bottom figure for the case  $V_{POS}$ = +15V and  $V_{NEG}$  = -10V

- For  $v_{IN}$  between -10 and +15 volts,  $v_{OUT} = v_{IN}$

- > If  $v_{IN}$  exceeds +15V, the output saturates at  $V_{POS}$

- > If  $v_{IN}$  < -10V, the output saturates at  $V_{NEG}$

- Since the input current is zero giving zero input power, the voltage follower can provide a large power gain

- Example 2.3 in text.

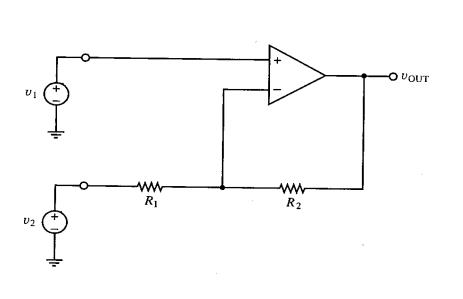

#### **Op-amp Difference Amplifier**

- The "difference amplifier" shown at the left-top combines both the inverting and non-inverting op-amps into one circuit

- Using superposition of the results from the two previous cases, we can write

- $\succ$  v<sub>OUT</sub> = [(R1 + R2)/R1]v<sub>1</sub> − (R2/R1)v<sub>2</sub>

- The gain factors for both inputs are different, however

- We can obtain the same gain factors for both v<sub>1</sub> and v<sub>2</sub> by using the modified circuit below

- Here the attenuation network at v<sub>1</sub> delivers a reduced input v+ = v<sub>1</sub>(R2/(R1 + R2))

- Replacing v<sub>1</sub> in the expression above by the attenuation factor, gives us

$v_{OUT} = (R2/R1)(v_1 - v_2)$

The difference amplifier will work properly if the attenuation network resistors (call them R3 & R4) are related to the feedback resistors R1 & R2 by the relation R3/R4 = R1/R2 (i.e. same ratio)

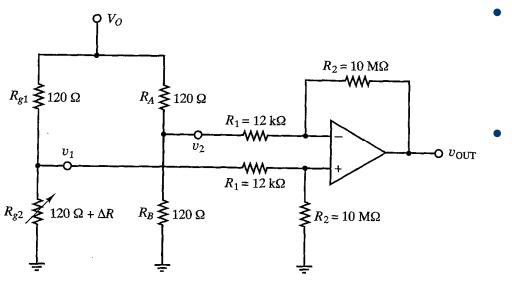

#### Ex. Difference Amplifier with a Resistance Bridge

The example of Fig's 2.14 and 2.15 in the text shows a difference amplifier used with a bridge circuit and strain gauge to measure strain.

#### Operation:

- The amplifier measures a difference in potential between v1 and v2.

- > By choosing  $R_A = R_B = Rg$  (unstressed resistance of Rg1 and Rg2), it is possible to obtain an approx linear relationship between  $v_{OUT}$  and  $\Delta L$ , where  $\Delta L$  is proportional to the strain across the gauge.

- Design:

- In order for the bridge to be accurate, the input resistances of the difference op-amp must be large compared to R<sub>A</sub>, R<sub>B</sub>, & Rg

- Input resistance at v1 (with v2 grounded) is R1 + R2 =~ 10 Mohm

- Input resistance at v2 (with v1 grounded) is just R1 = 12 K due to the v1-v2 virtual short

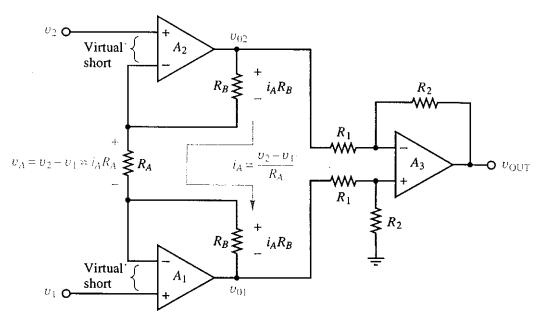

#### **Instrumentation Amplifier**

- Some applications, such as an oscilloscope input, require differential amplification with extremely high input resistance

- Such a circuit is shown at the left

- A3 is a standard difference op-amp with differential gain R2/R1

- A1 and A2 are additional op-amps with extremely high input resistances at v1 and v2 (input currents = 0)

- Differential gain of input section:

- Due to the virtual shorts at the input of A1 and A2, we can write  $i_A = (v2 v1) / R_A$

- Also,  $i_A$  flows through the two  $R_B$  resistors, allowing us to write  $v_{02} v_{01} = i_A(R_A + 2R_B)$

- Combining these two equations with the gain of the A3 stage, we can obtain

$$v_{OUT} = (R2/R1)(1 + [2R_B/R_A])(v1 - v2)$$

By adjusting the resistor R<sub>A</sub>, we can adjust the gain of this instrumentation amplifier

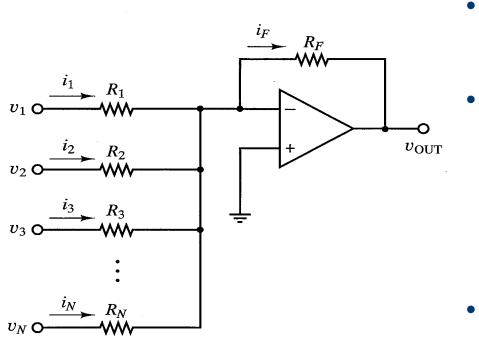

#### **Summation Amplifier**

- A summation op-amp (shown at left) can be used to obtain a weighted sum of inputs  $v1...v_N$

- > The gain for any input k is given by  $R_F/R_k$

- If any input goes positive, v<sub>OUT</sub> goes negative just enough to force the input v- to zero, due to the virtual short nature of the op-amp

- > Combining all inputs, we have

- $v_{OUT} = -R_F(v_1/R_1 + v_2/R_2 + ... + v_N/R_N)$

- The input resistance for any input k is given by R<sub>k</sub> due to the virtual short between v- and v+

- Example 2.5 use as an audio preamp with individual adjustable gain controls

- Note effect of microphone's internal resistance

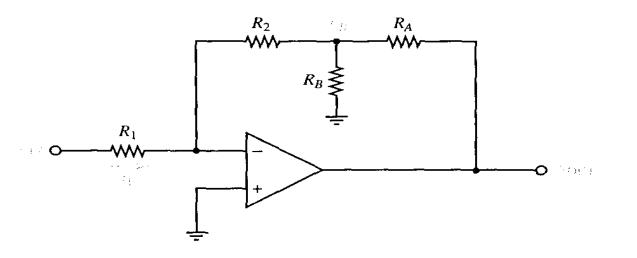

#### **Op-amp with T-bridge Feedback Network**

- To build an op-amp with high closed-loop gain may require a high value resistor R2 which may not be easily obtained in integrated circuits due to its large size

- A compromise to eliminate the high value resistor is the op-amp with T-bridge feedback network, shown below

- >  $R_A$  and  $R_B$  comprise a voltage divider generating node voltage  $v_B = v_{OUT} R_B / (R_A + R_B)$ , assuming that R2 >>  $R_A ||R_B$

- > Since  $v_B$  is now fed back to v-, an apparent gain  $v_B/v_{IN} = -(R2/R1)$  can be written

- Combining these two equations allows us to write  $v_{OUT} = (R2/R1)([R_A + R_B]/R_B)v_{IN}$

- Fairly large values of closed-loop gain can be realized with this network without using extremely large IC resistors

R. W. Knepper SC412, slide 2-13

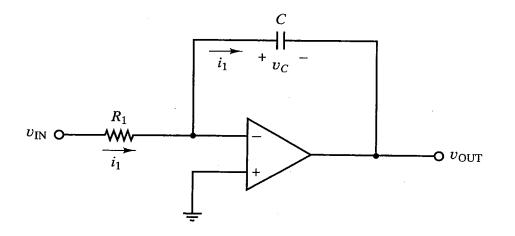

#### **Op-amp Integrator Network**

- Shown below is an op-amp integrator network

- The output will be equal to the integral of the input, as long as the op-amp remains in its linear region

- > Due to the virtual short property of the op-amp input, we can write  $i_1 = v_{IN}/R_1$

- > This current  $i_1$  starts charging the capacitor C according to the relation  $i_1 = C(dv_C/dt)$

- Since v- remains at GND, the output drops below GND as C charges and the time derivative of  $v_{OUT}$  becomes the negative of the time derivative of  $v_C$

$\succ$  since v<sub>c</sub> = 0 - v<sub>OUT</sub>

• Combining the above equations, we obtain

$$\blacktriangleright dv_{OUT}/dt = -i_1/C = -v_{IN}/R_1C$$

- Solving for v<sub>OUT</sub>(t) and assuming C is initially uncharged, we obtain

- $\succ$  v<sub>OUT</sub>(t) = (-1/R<sub>1</sub>C) / v<sub>IN</sub> dt where the integral is from 0 to t

R. W. Knepper SC412, slide 2-14

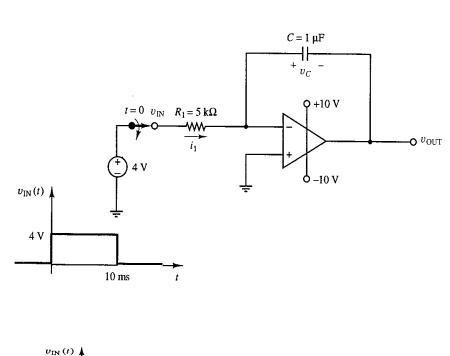

### **Op-amp Integrator Example**

- Given an input signal of 4V square wave for 10 ms duration, what is the integrator output versus time for the integrator circuit at the left?

- The current into the capacitor during the square wave is constant at 4V/5Kohm = 0.8 mA

- Using the integral expression from the previous chart, the capacitor voltage will increase linearly in time (1/R<sub>1</sub>C) 4t = 0.8t V/ms during the square wave duration

- The output will therefore reduce linearly in time by - 0.8t V/ms during the pulse duration, falling from 0 to -8 volts, as shown in the figure at left

- Since at 10 ms the output will be -8 V > V<sub>NEG</sub>, the op-amp will not saturate during the 10 ms input pulse

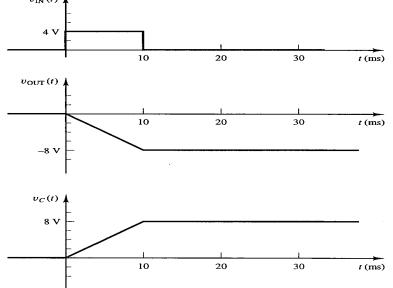

### **Op-amp Integrator Example with Long Pulse**

- Consider a case with an infinitely long 4V pulse

- The capacitor will continue to charge linearly in time, but will eventually reach 10V which will force v<sub>OUT</sub> to -10V (= V<sub>NEG</sub>) and saturate the op-amp (at 12.5 ms)

- > After this time, the op-amp will no longer be able to maintain v- at 0 volts

- Since v<sub>OUT</sub> is clamped at –10V, the capacitor will continue to charge exponentially with time constant R<sub>1</sub>C until v- = +4V

- During this time the capacitor voltage will be given by

$v_{c}(t) = 10 + 4[1 - exp(t_{1} - t)/R_{1}C]$  where  $t_{1} = 12.5$  ms

- At  $t = t_1$ ,  $v_c = 10$  V and at t = infinity,  $v_c = 14$  V

- > The resulting capacitor and output waveforms are shown below.

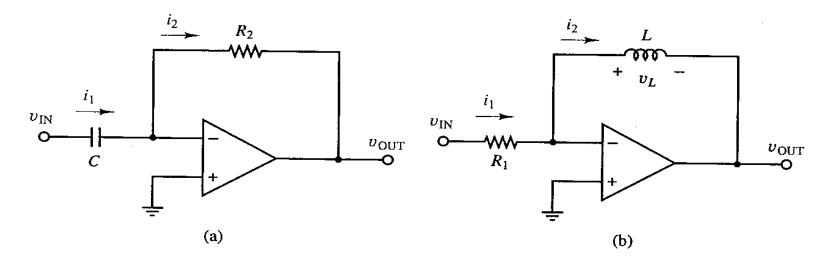

#### **Op-amp as a Differentiator**

- The two op-amp configurations shown below perform the function of differentiation

- The circuit on the left is the complement of the integrator circuit shown on slide 2-14, simply switching the capacitor and resistor

- > The circuit on the right differentiates by replacing the capacitor with an inductor

- For the circuit on the left we can write

►

$$i_1 = C(dv_{IN}/dt) = i_2 = (0 - v_{OUT})/R2$$

or

$v_{OUT} = -R_2C (dv_{IN}/dt)$

• Similarly, for the circuit on the right we can obtain

$v_{OUT} = -(L/R_1)(dv_{IN}/dt)$

- By nature a differentiator is more susceptible to noise in the input than an integrator, since the slope of the input signal will vary wildly with the introduction of noise spikes.

- Do exercises 2.23 and 2.25.

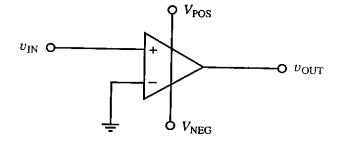

### Non-Linear Op-amp Circuits

- Op-amps are sometimes used in non-linear open-loop configurations where the slightest change in  $v_{IN}$  will force the op-amp into saturation ( $V_{POS}$  or  $V_{NEG}$ )

- Such non-linear op-amp uses are often found in signal processing applications

- Two examples of such non-linear operation are shown at the left

- Left-top is an open-loop polarity indicator

- If  $v_{IN}$  is above or below GND by a few mV,  $v_{OUT}$  is forced to either positive or negative rail voltage

- Left-bottom is an open-loop comparator

- If v<sub>IN</sub> is above or below V<sub>R</sub> by a few mV, v<sub>OUT</sub> is forced to the positive or negative rail voltage

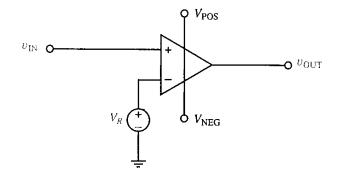

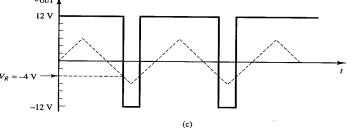

#### **Open-Loop Comparator** (Example 2.8 in text)

- Given the open-loop comparator shown at the left with  $V_{POS}$ = +12V and  $V_{NEG}$ = -12V, plot the output waveforms for  $V_R$  = 0, +2V, and -4V, assuming  $v_{IN}$  is a 6V peak triangle wave

- The solution is shown at the left

- In (a) the output switches symmetrically from VPOS rail to V<sub>NEG</sub> rail as the input moves above or below GND

- In (b) the output switches between the rail voltages as the input goes above or below +2 V

- In (c) the output switches between the rail voltages as the input varies above or below –4 V

- The output becomes a pulse generator with adjustable pulse width

- Do Exercise 2.28.

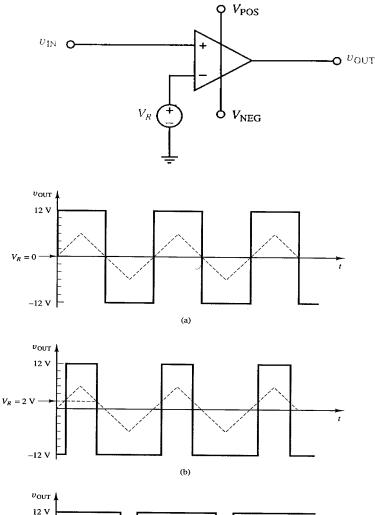

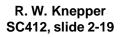

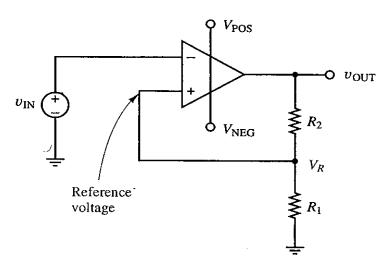

### Schmitt Trigger Op-amp Circuit

- The open-loop comparator from the previous two slides is very susceptible to noise on the input

- Noise may cause it to jump erratically from + rail to rail voltages

- The Schmitt Trigger circuit (at the left) solves this problem by using positive feedback

- It is a comparator circuit in which the reference voltage is derived from a divided fraction of the output voltage, and fed back as positive feedback.

- The output is forced to either V<sub>POS</sub> or V<sub>NEG</sub> when the input exceeds the magnitude of the reference voltage

- The circuit will remember its state even if the input comes back to zero (has memory)

- The transfer characteristic of the Schmitt Trigger is shown at the left

- Note that the circuit functions as an inverter with hysteresis

- > Switches from + to rail when  $v_{IN} > V_{POS}(R1/(R1 + R2))$

- Switches from to + rail when  $v_{IN} < V_{NEG}(R1/(R1 + R2))$

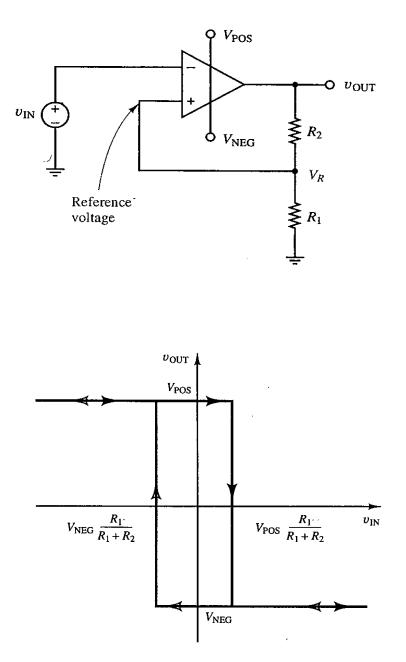

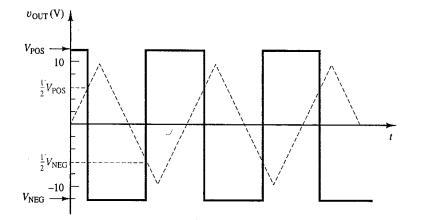

### Schmitt Trigger Op-amp Example (2.9 in text)

- Assume that for the Schmitt trigger circuit shown at the left,  $V_{POS}/_{NEG} = +/-12$  volts, R1 = R2, and  $v_{IN}$  is a 10V peak triangular signal. What is the resulting output waveform?

- Answer:

- The output will switch between +12 and -12 volts

- The switch to V<sub>NEG</sub> occurs when v<sub>IN</sub> exceeds V<sub>POS</sub>(R1/(R1 + R2)) = +6 volts

- The switch to V<sub>POS</sub> occurs when v<sub>IN</sub> drops below V<sub>NEG</sub>(R1/R1 + R2)) = -6 volts

- See waveforms at left

- Consider the case where we start out the Schmitt Trigger circuit with  $v_{IN} = 0$  and  $v_{OUT} = 0$  (a quasistable solution point for the circuit)

- However, any small noise spike on the input will push the output either in the + or – direction, causing v+ to also go in the same direction, which will cause the output to move further in the same direction, etc. until the output has become either V<sub>POS</sub> or V<sub>NEG</sub>.

## Non-Ideal Properties of Op-amps:

#### **Output Saturation and Input-Offset Voltage**

#### **Output Saturation Voltage**

- Although we have been assuming the op-amp will saturate at the supply voltages V<sub>POS</sub> and V<sub>NEG</sub>, in actual practice an op-amp circuit will saturate at somewhat lower than V<sub>POS</sub> and higher than V<sub>NEG</sub>, due to internal voltage drops in the design

- Emitter-follower output stage (BJT design) will drop a V<sub>BE</sub>

- CMOS design will have a similar drop

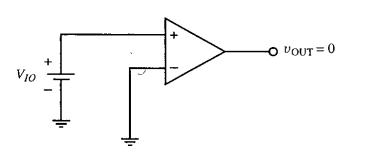

#### Input-Offset Voltage

- We have been assuming v+ = v- when v<sub>OUT</sub> = 0. In actual practice, however, there is usually a small input (or output) dc offset voltage in order to force v<sub>OUT</sub> to 0, under open-loop operation.

- The input-offset voltage (labeled V<sub>IO</sub> in the figure at the left) can be positive or negative and is usually small (anywhere from 1 uV to 10 mV)

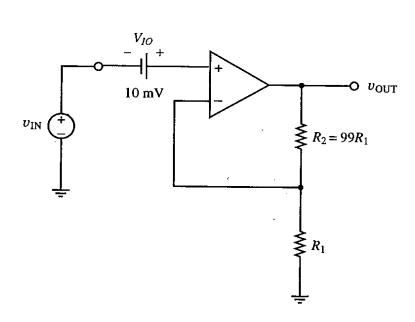

### Input-Offset Voltage Effect on Output Voltage

• To examine the effect input-offset voltage has on the output voltage, consider the non-inverting op-amp

- > The gain of the op-amp is (R1 + R2)/R1 = 100

- Assume the input voltage is modeled adequately by a source V<sub>IO</sub> = +/- 10 mV

> Then, we can write that the output voltage is given by  $(y_1, y_2) = (y_1, y_2) + (y_2) + ($

$v_{OUT} = (v_{IN} + V_{IO})(R1 + R2)/R1$ = 100  $v_{IN}$  +/- 1 volt

Thus, a 10 mV input-offset causes a 1V offset in v<sub>OUT</sub>

<u>Exercise 2.32</u>: Show that the above equation applies even if V<sub>IO</sub> is placed in series with the v- input, instead of the v+ input.

Using the virtual short condition, we can write

$v_{OUT}[R1/(R1 + R2)] + V_{IO} = v_{IN}$  or

$v_{OUT} = (R1 + R2)/R1)(v_{IN} + V_{IO})$  → same as above!

- <u>Exercise 2.33</u>: What is the output of an inverting opamp if the effect of input offset is considered?

- > Based on the inverting op-amp circuit of slide 2-6, we can write  $i_1 = (v_{IN} V_{IO})/R1 = i_2 = (V_{IO} v_{OUT})/R2$

> or,  $v_{OUT} = - (R2/R1) v_{IN} + V_{IO} (R1 + R2)/R1$

## **Output-Offset Voltage and Nulling Out Offset**

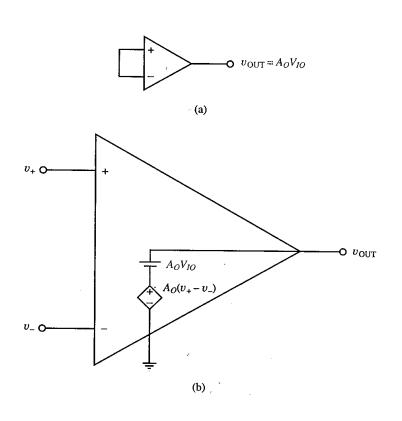

- A parameter called the **output-offset voltage** may be used to represent the internal imbalance of an op-amp, rather than the input-offset voltage

- The output-offset voltage is defined as the measured output voltage when the input terminals are shorted together, as shown at the left-top fig.

- The output-offset voltage may be modeled by placing a voltage source A<sub>o</sub>V<sub>IO</sub> in series with the output voltage source A<sub>o</sub>(v<sub>+</sub> - v<sub>-</sub>)

- Consequently, the output-offset voltage is essentially the input-offset voltage multiplied by the open loop gain.

- Do exercise 2.34

- How can we correct for offset voltage?

- Some op-amps provide two terminals (offset-null terminals) for adjusting out the offset voltage

- A potentiometer is connected across the offset null terminals with the  $V_{\rm NEG}\, {\rm supply}\,\, {\rm voltage}\,\, {\rm connected}\,\, {\rm to}\,\, {\rm the}\,\, {\rm adjustable}\,\, {\rm center}\,\, {\rm tap}$

- If the op-amp does not have an internal null adjustment provision, an external adjustment similar to that shown in Example 2.11 can be provided.

- Look at Exercise 2.36 (error in text)

## Effect of Non-zero Input Bias Currents

R. W. Knepper SC412, slide 2-25

- In practice op-amps do not actually have zero input currents, but rather have very small input currents labeled I<sub>+</sub> and I<sub>-</sub> in the figure at the left

- Modeled as internal current sources inside op-amp

- >  $I_+$  and  $I_-$  are both the same polarity

- e.g. if the input transistors are NPN bipolar devices, positive  $I_+$  and  $I_-$  are required to provide base current

- In order to allow for slightly different values of I<sub>+</sub> and I<sub>-</sub>, we define the term I<sub>BIAS</sub> as the average of I<sub>+</sub> and I<sub>-</sub>

$$|_{\text{BIAS}} = \frac{1}{2} \left( \mathbf{I}_{+} + \mathbf{I}_{-} \right)$$

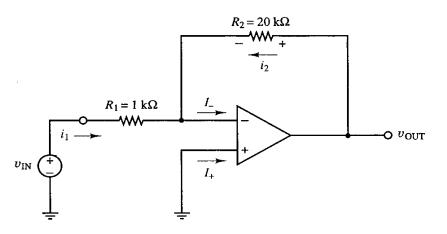

- Example: Given the op-amp shown in the bottom left figure, derive an expression for v<sub>out</sub> that includes the effect of input bias currents

- Assume  $I_{+} = I_{-} = 100 \text{ nA}$

- ➢ Using the virtual short condition and KCL, we can write  $v_{IN}/R1 = I_1 + (0-v_{OUT})/R2$  or

$v_{OUT} = -(R_2/R_1)v_{IN} + I_R_2$

- > Plugging in values gives  $v_{OUT} = -20 v_{IN} + 2 mV$

- Do exercise 2.38, p. 77

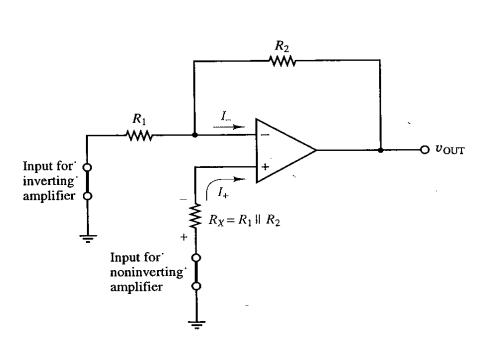

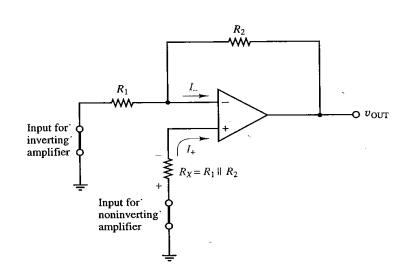

### **Correcting for Non-zero Input Bias Current**

R. W. Knepper SC412, slide 2-26

- The effect of non-zero input bias current can be zero'ed out by inserting a resistor R<sub>x</sub> in series with the V+ input terminal (as shown)

- This same correction works for both inverting and non-inverting op-amps

- We choose Rx such that the dc component on the output caused by I+ exactly cancels the dc component on v<sub>OUT</sub> caused by I-

- One can use either KCL (Kirchhoff's Current Law) or superposition to show that choosing Rx = R1 || R2 completely cancels out the dc effect of non-zero input bias current

- KCL Method (inverting op-amp at left)

- $\succ$  v<sub>IN</sub> is applied to R1 and Rx is grounded

- $\blacktriangleright$  v- = v+ = 0 I<sub>+</sub>R<sub>x</sub> due to virtual short

- Apply KCL to v+ input:

$(v_{IN} - v_{.})/R1 = I_{.} + (v_{.} - v_{OUT})/R2$

> Solve for  $v_{OUT}$  and substitute  $-I_+R_x$  for  $v_-$

$v_{OUT} = - (R2/R1) v_{IN} + I_R2 - I_+R_x(R1 + R2)/R1$

Setting the dc bias terms equal yields

Rx = R1 || R2 = R1 R2/(R1 + R2)

## Input Offset Current Definition

- Non-zero input bias currents I+ and I- may not always be equal (some opamps)

- Variation in bipolar transistor beta may cause base currents to non-track, or perhaps there are circuit design issues causing non equal offset I

- We define a parameter "input offset current"

$\mathbf{I}_{\mathrm{IO}} = \mathbf{I}_{+} - \mathbf{I}_{-}$

- Typical values of I<sub>IO</sub> are 5-10% (of I-) although it can be as high as 50%

- Example 2.13 based on figure at left

- ➢ R1 = 1K, R2 = 20K ohms

- > Assuming Ibias = 1 uA and  $I_{IO}$  = 100 nA, find I+, I-, and the effect of  $I_{IO}$  on vout

- Since (I<sub>+</sub> + I<sub>-</sub>)/2 = 1 uA and I<sub>+</sub> I<sub>-</sub> = 0.1uA, we can solve for I+ = 1.05 uA and I- = 0.95 uA

- Using the expression for Vout from slide 2-26 with Vin = 0 and Rx = R1 || R2 gives us

- $\succ$  v<sub>OUT</sub> = R2 (I<sub>−</sub> I<sub>+</sub>) = -I<sub>IO</sub> R2 = -2 mV

- Do Exercise 2.40

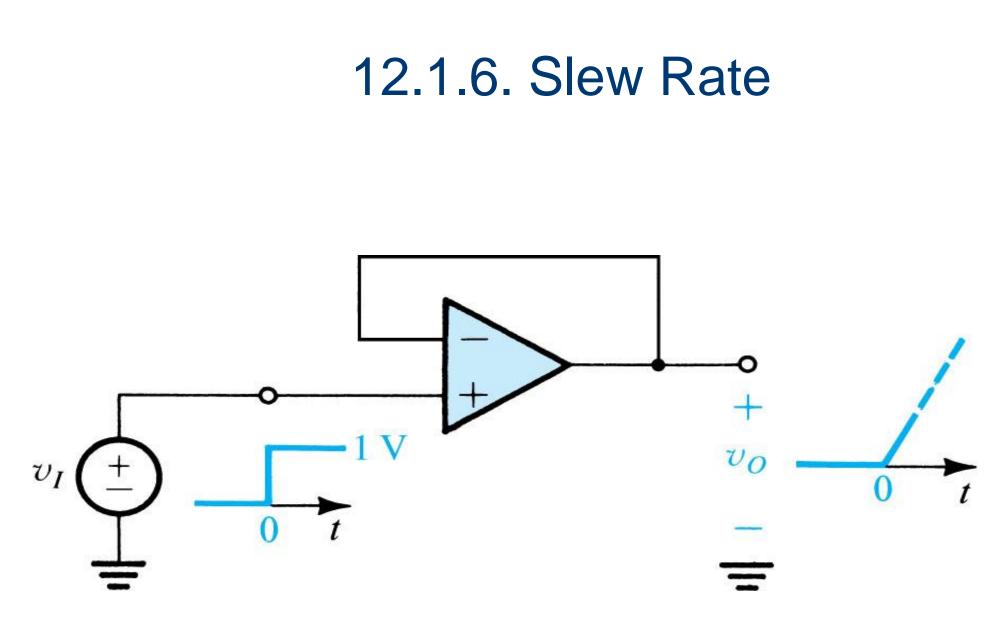

## Slew Rate Limitation in an Op-amp

• A real op-amp is limited in its ability to respond instantaneously to an input signal with a high rate of change of its input voltage. This limitation is called the **slew rate**, referring to the maximum rate at which the output can be "slewed".

> Typical slew rates may be between  $1-10 \text{ V/}\mu\text{s} = 1E6 - 1E7 \text{ V/s}$

- > Max slew rate is a function of the device performance of the op-amp components & design

- > If the input is driven above the slew rate limit, the output will exhibit non-linear distortion

- Slew rate limitation behavior: (Example 2.14):

- Assume an inverting op-amp with a gain of –10 has a max slew rate of 1 V/µs and is driven by a sinusoidal input with a peak of 1V. At what input frequency will the output start to show slew rate limitation?

- Output has a peak of 10 volts since gain is -10 and input peak is 1 volt

- If the input is given by  $v_{IN} = Vo \sin \omega t$ , the max slope will occur at t=0 and will be given by d (Vo sin  $\omega t$ )/dt |(t=0) =  $\omega Vo = 2\pi f Vo$

- The max frequency is therefore given by

$f_{max} = slew rate/2\pi V_o = 1E6 V/s / 2\pi 10V = ~ 16 kHz$

Note: This surprisingly low max frequency is directly proportional to the slew rate limit spec and inversely proportional to the peak output voltage!

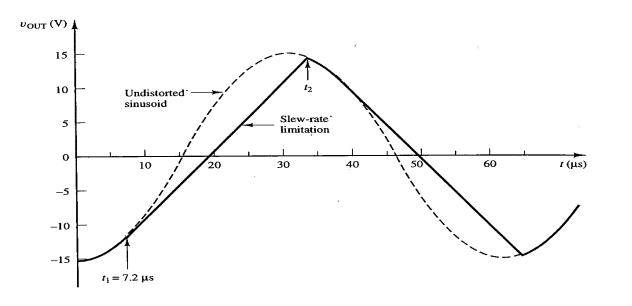

### Slew Rate Limitation in an Op-amp

Exceeding the slew rate limitation (Example 2.14b):

- If the inverting op-amp from 2.14a (with gain = -10 and slew rate =  $1 \text{ V/}\mu\text{s}$ ) is driven by a 16 kHz sinusoidal input with a peak of 1.5V, what is the effect on the output waveform?

- Since we are now exceeding the slew rate limit, the output will be distorted

- > Let  $v_{OUT} = -Vo \cos \omega t$  (for visual simplicity) where  $Vo = 10 \times 1.5V = 15V$

- > Then  $dv_{OUT}/dt = \omega Vo \sin \omega t$

- > Above some  $t = t_1$  the slew rate will limit the output response

$t_1 = (1/\omega) \sin^{-1} (\text{slew rate}/\omega \text{Vo}) = (1/2\pi \ 16 \text{ kHz}) \sin^{-1} (1\text{E}6 / 2\pi \ 16 \text{ kHz} \ \text{x} \ 15\text{V}) = 7.2 \ \mu\text{s}$

> The resulting waveform is shown below. At  $t_1$  the slew-limited output can't keep up with the input until it catches up at  $t_2$ , when the cycle starts all over again.

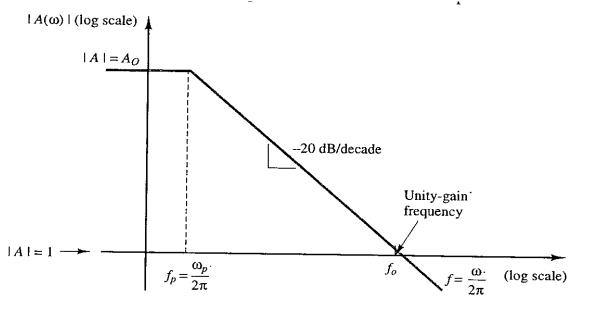

#### Frequency Response of an Op-amp

- An open-loop op-amp has a constant gain Ao only at low frequencies, and a continuously reducing gain at higher frequencies due to internal device and circuit inherent limits.

- > For a single dominant pole at freq  $f_p$ , the frequency-dependent gain A(j $\omega$ ) can be written as

$A(j\omega) = Ao/[1 + j\omega/\omega_p] = Ao/[1 + jf/f_p]$  where  $\omega_p = 2\pi f_p$

- $\succ$  the gain rolls off at 20dB/decade for frequencies above f<sub>p</sub>, as shown below

- An op-amp may have additional higher frequency poles, as well, but is often described over a large frequency range by the dominant pole (as assumed in the figure below)

- The unity gain frequency  $f_o$  is defined as the frequency where the gain = 1

- For the single dominant pole situation assumed in the figure below, f<sub>o</sub> can be found by extrapolating the 20 dB/decade roll-off to the point where the gain is unity.

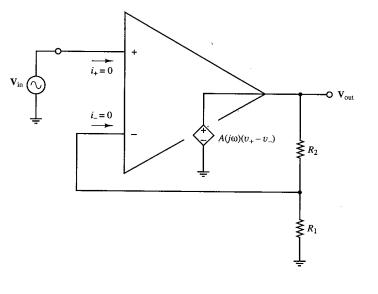

#### Frequency-Dependent Closed-Loop Gain

• The effect of the frequency-dependent open-loop gain on the closed-loop gain can easily be found by deriving  $v_{OUT}(j\omega)$  as a function of the open-loop gain  $A(j\omega)$  in the op-amp configuration shown at the left

$$v_{OUT} = A(j\omega) (v+ - v-)$$

=  $A(j\omega) [v_{IN} - v_{OUT}(R1/(R1 + R2))]$ , or

- $v_{OUT} = A(j\omega)/[1 + A(j\omega)\beta]$  where

- $\beta$  = R1 / (R1 + R2) is the closed-loop feedback function

- Substituting A(jw) into the above equation gives us the complete frequency dependent result for the closed loop gain

$$v_{OUT}/v_{IN} = Ao/[1 + Ao\beta + j\omega/\omega_p]$$

= [Ao/(1 + Aoβ)]/[1 + jω/ω<sub>p</sub>(1 + Aoβ)]

• The dc gain is given by

> Ao/(1 + Ao $\beta$ ) = ~ 1/ $\beta$  = (R1 + R2)/R1

- The closed-loop response is seen to contain a single pole at  $\omega_{fb} = \omega_p (1 + Ao\beta) >> \omega_p$

- > Closed-loop BW = ~  $A_o\beta$  x open-loop BW

## **Gain-Bandwidth Product**

• Multiplication of the closed-loop BW by the closed-loop gain gives us

$[Ao/(1+Ao\beta)]\omega_{fb} = [Ao/(1+Ao\beta)]\omega_p(1+Ao\beta)$

$$= Ao\omega_{I}$$

- which is the open-loop gain-BW product

- For the assumption of a single dominant pole and very high Ao, the gain-bandwidth product is a constant

- Unity-gain frequency  $\omega_o$  (=  $2\pi f_o$ ) is the freq where the op-amp response extrapolates to a gain of 1

- > we can show that  $\omega_o = A_o \omega_p$  (for a system with a single dominant pole)

#### **Op-amp Output Current Limit:**

- A typical op-amp contains circuitry to limit the output current to a specified maximum in order to protect the output stage from damage

- If a low value load impedance is utilized, the output current limit may be reached before the output saturates at the rail voltage, forcing the op-amp to lower gain

- See Example 2.15

# UNIT - IV

#### STABILITY AND FREQUENCY COMPENSATION

# Introduction

#### • IN THIS CHAPTER YOU WILL LEARN

- The design and analysis of the two basic CMOS op-amp architectures: the two-stage circuit and the single-stage, folded cascode circuit.

- The complete circuit of an analog IC classic: the 741 op-amp. Though 40 years old, the 741 circuit includes so many interesting and useful design techniques that its study is still a must.

- Applications of negative feedback within op-amp circuits to achieve bias stability and increased CMRR.

# Introduction

#### • IN THIS CHAPTER YOU WILL LEARN

- How to break a large analog circuit into its recognizable blocks, to be able to make the analysis amendable to a pencil-and-paper approach – which is the best way to learn design.

- Some of the modern techniques employed in the design of low-voltage single-supply BJT op amps.

- Most importantly, how the different topics we learned about in the preceding chapters come together in the design of the most important analog IC – the op amp.

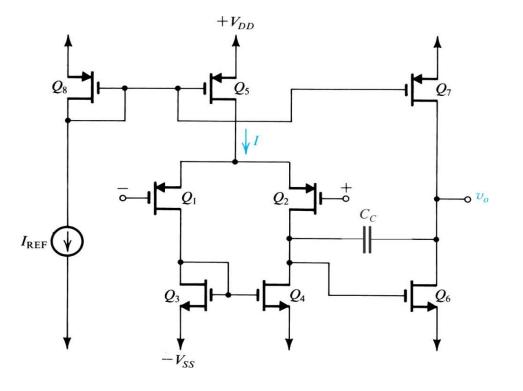

# 12.1. The Two Stage CMOS Op Amp

- Two-stage op amp is shown in Figure 12.1.

- It was studied in Section 8.6.1 as example of multi-stage CMOS amplifier.

Figure 12.1 The basic two-stage CMOS op-amp configuration.

# 12.1.1. The Circuit

- Two Stages:

- > Differential Pair  $Q_1/Q_2$ .

- Biased by current source Q<sub>5</sub>

- Fed by a reference current  $I_{REF}$

- > Current Mirror Load  $Q_3/Q_4$ .

- Frequency Compensation

- Voltage Gain 20V/V to 60V/V

- Reasonable Common-Mode Rejection Ratio (CMRR)

#### 12.1.1. Input Common-Mode Range and Output Swing

(eq12.1) dc offset elimination:  $\frac{(W/L)_{6}}{(W/L)_{4}} = 2\frac{(W/L)_{7}}{(W/L)_{5}}$ (eq12.2) common-mode input:  $V_{ICM} \ge -V_{SS} + V_{tn} + V_{OV3} - |V_{tp}|$ (eq12.3) common-mode input:  $V_{ICM} \le -V_{DD} + |V_{OV5}| - |V_{tp}| - |V_{OV1}|$ (eq12.4)  $-V_{SS} + V_{OV3} + V_{tn} - |V_{tp}| \le V_{ICM} - |V_{tp}| - |V_{OV1}| - |V_{OV5}|$ (eq12.5)  $-V_{SS} + V_{OV6} \le V_{0} \le V_{DD} - |V_{OV7}|$

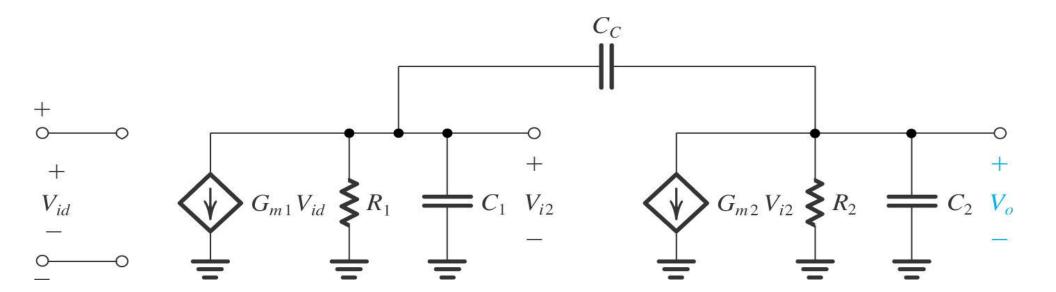

# 12.1.3. Voltage Gain

- Consider simplified equivalent circuit model for small-signal operation of CMOS amplifier.

- ➢ Figure 12.2.

- Input resistance is practically infinite (*R<sub>in</sub>*).

- First-stage transconductance  $(G_{m1})$  is equal to values for  $Q_1$  and  $Q_2$ .

- Since Q<sub>1</sub> and Q<sub>2</sub> are operated at equal bias currents (I/2) and equal overdrive voltages, equation (12.7) applies.

#### 12.1.1. Input Common-Mode Range and Output Swing

(eq12.7) stage-one transconductance:  $G_{m1} = \frac{2(1/2)}{V_{OV1}} = \frac{1}{V_{OV1}}$

(eq12.8)

$$R_1 = r_{o2} || r_{o4}$$

(eq12.9)  $r_{o2} = |V_{A2}|/(1/2)$

(eq12.10)  $r_{o4} = |V_{A4}|/(1/2)$

(eq12.11) gain of first stage:  $A_1 = -G_{m1}R_1$

(eq12.12) gain of first stage:  $A_1 = -gm1(r_{o2} || r_{o4})$

(eq12.13) gain of first stage:  $A_1 = -\frac{2}{V_{OV1}}/\left(\frac{1}{|V_{A2}|} + \frac{1}{|V_{A4}|}\right)$

(eq12.14) stage-two transconductance:  $G_{m2} = g_{m6} = \frac{2I_{D6}}{V}$ (eq12.15)  $R_2 = r_{06} || r_{07}$ (eq12.16)  $r_{o6} = |V_{A6}| / I_{D6}$ (eq12.17)  $r_{04} = |V_{A7}| / I_{D7} = |V_{A7}| / I_{D6}$ (eq12.18) voltage gain of second stage:  $A_2 = -G_{m_2}R_2$ (eq12.19) voltage gain of second stage:  $A_2 = -g_{mb}(r_{ob} | | r_{o7})$ (eq12.20) voltage gain of second stage:  $A_2 = -\frac{2}{V_{OV6}} / \left(\frac{1}{V_{A6}} + \frac{1}{|V_{A7}|}\right)$ (eq12.21) overall dc gain:  $A_{\nu} = G_{m1}R_1G_{m2}R_2$ (eq12.22) overall dc gain:  $A_v = g_{m1}(r_{o2} | | r_{o4})g_{m6}(r_{o6} | | r_{o7})$ (eq12.21) output resistance:  $R_o = r_{o6} || r_{o7}$

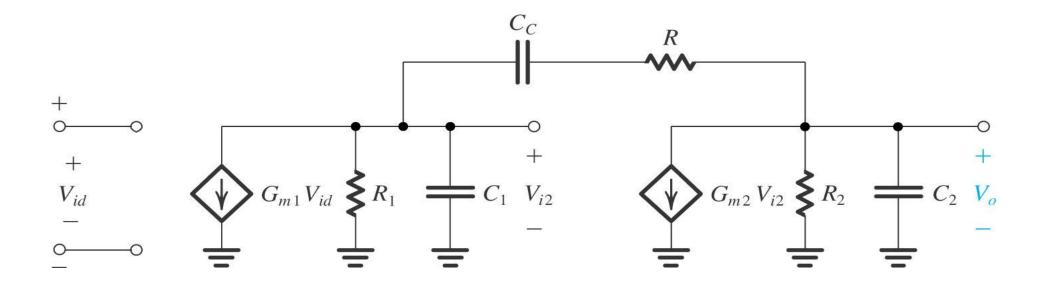

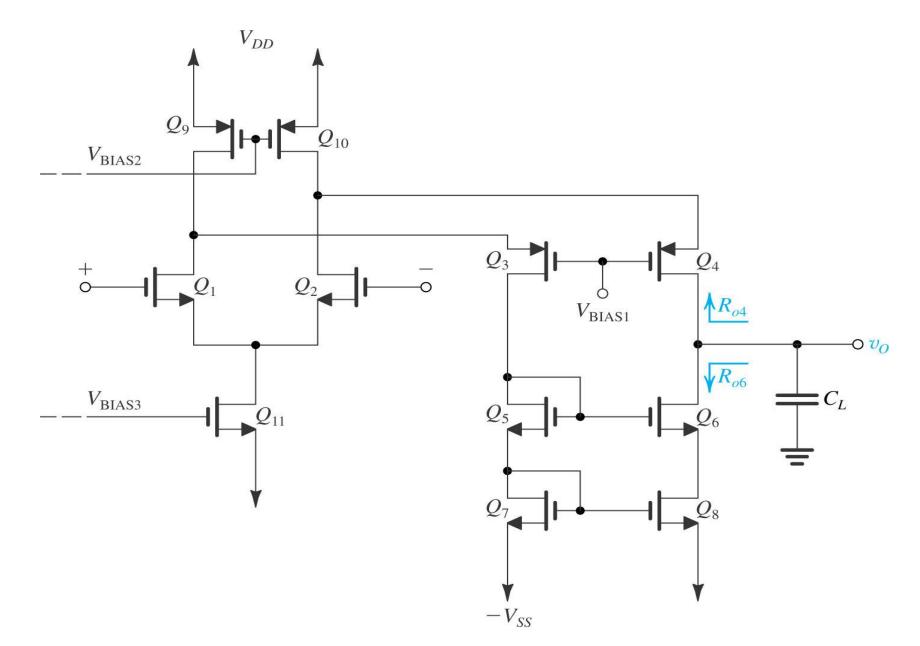

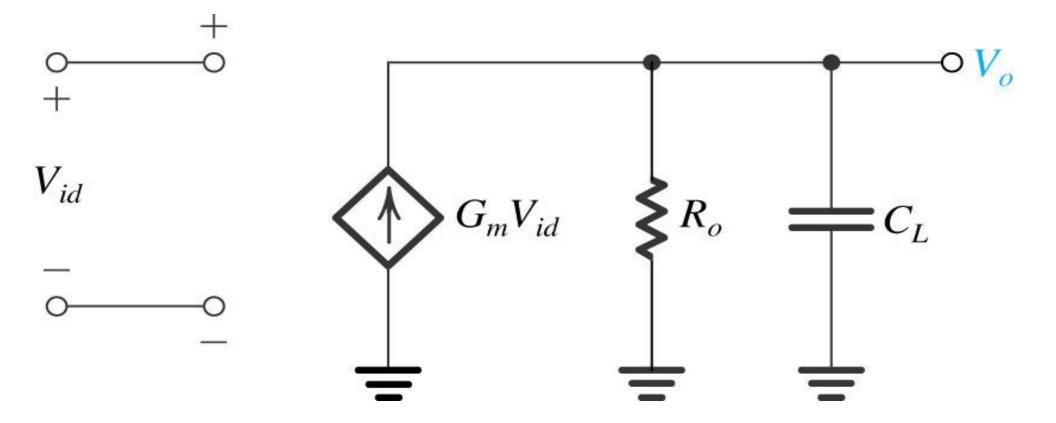

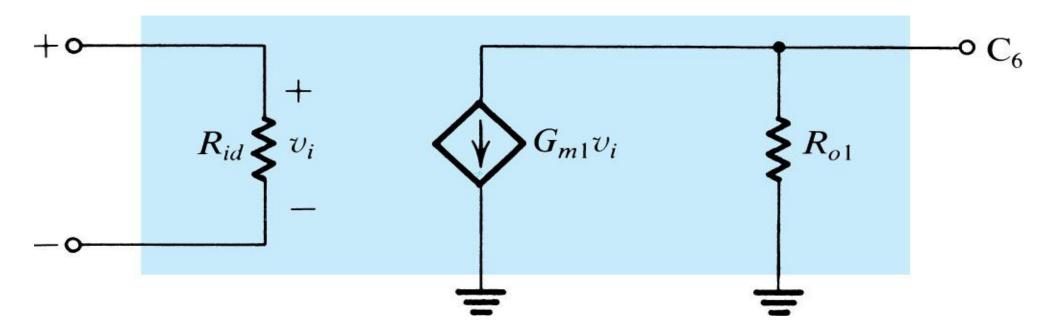

#### Figure 12.2: Small-signal equivalent circuit for the op amp in Fig. 12.1.

#### 12.1.4. Common-Mode Rejection Ratio

- CMRR of two-stage amplifier is determined by first stage

▷ CMRR = [g<sub>m1</sub>(r<sub>o2</sub>||r<sub>o4</sub>)[2g<sub>m3</sub>R<sub>SS</sub>]

- RSS is output resistance of the bias source  $Q_5$

- CMRR is of the order of (g<sub>m</sub>r<sub>o</sub>)<sup>2</sup>

➤ This is high.

- $G_m r_o$  is proportional to  $V_A / V_{OV}$

- CMRR is increased if long channels are used.

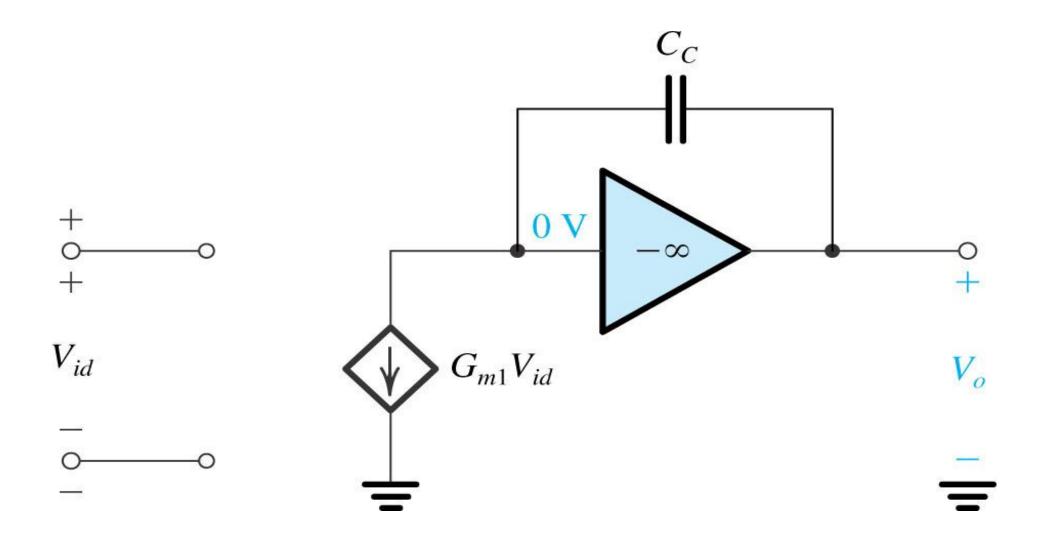

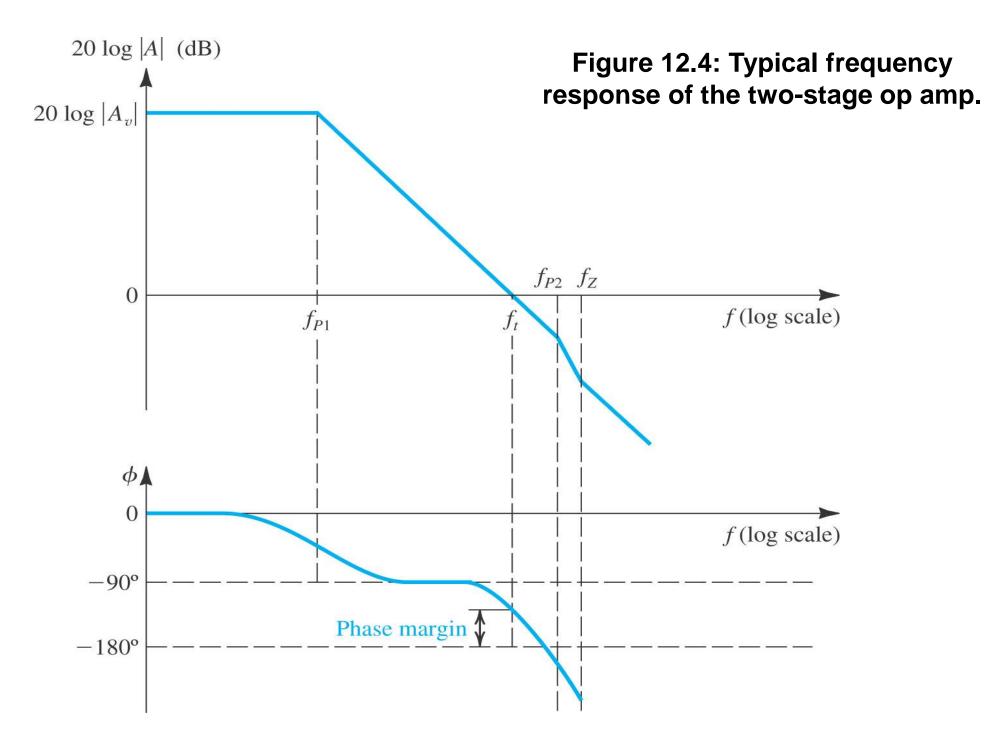

## 12.1.5. Frequency Response

$$\begin{array}{l} (\text{eq12.25}) \ C_{1} = C_{gd2} + C_{db2} + C_{gd4} + C_{db4} + C_{gs6} \\ (\text{eq12.26}) \ C_{2} = C_{db6} + C_{db7} + C_{gd7} + C_{L} \\ (\text{eq12.30}) \ f_{t} = \left| A_{v} \right| \ f_{P1} \\ (\text{eq12.31}) \ f_{t} = \frac{G_{m1}}{2\pi R_{1}G_{m2}R_{2}C_{c}} \\ (\text{eq12.32}) \ f_{P2} = \frac{G_{m2}}{2\pi C_{2}} \\ (\text{eq12.33}) \ f_{P2} = \frac{G_{m2}}{2\pi C_{c}} \\ (\text{eq12.33}) \ G_{m1} < G_{m2} \\ (\text{eq12.33}) \ G_{m1} < G_{m2} \\ \end{array}$$

**Figure 12.3** An approximate high-frequency equivalent circuit of the two-stage op amp. This circuit applies for frequencies  $f \gg f_{P1}$ .

## 12.1.5. Frequency Response

(eq12.34)

$$\phi_{P2} = -\tan^{-1}\left(\frac{f_t}{f_{P2}}\right)$$

(eq12.36)  $\phi_Z = -\tan^{-1}\left(\frac{f_t}{f_Z}\right)$

(eq12.37)  $\phi_{\text{total}} = 90^{\circ} + \tan^{-1}\left(\frac{f_t}{f_Z}\right) + \tan^{-1}\left(\frac{f_t}{f_Z}\right)$

(eq12.38) phase margin =  $180^{\circ} - \phi_{\text{total}}$

Figure 12.5: Small-signal equivalent circuit of the op amp in Fig. 12.1 with a resistance *R* included in series with *CC*.

Figure 12.6: A unity-gain follower with a large step input. Since the output voltage cannot change immediately, a large differential voltage appears between the op-amp input terminals.

Figure 12.7: Model of the two-stage CMOS op-amp of Fig. 12.1 when a large differential voltage is applied.

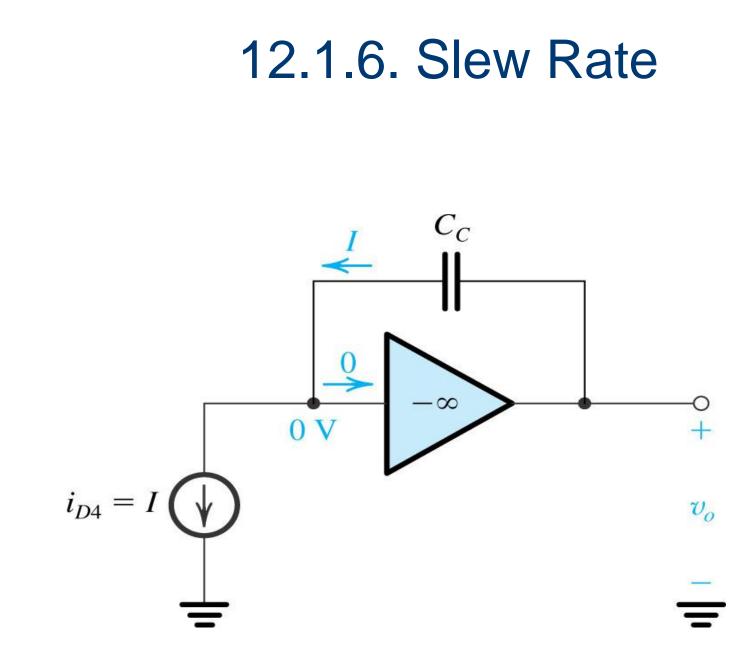

# Relationship Between SR and f<sub>t</sub>

- Simple relationship exists between unity-gain bandwidth  $(f_t)$  and slew rate.

- ➤ Equations (12.31) through (12.40).

- $SR = 2\pi f_t V_{OV}$

- Slew rate is determined by the overdrive voltage at which first-stage transistors are operated.

- For a given bias current *I*, a larger V<sub>OV</sub> is obtained if Q<sub>1</sub> and Q<sub>2</sub> are *p*-channel devices.

# 12.1.7. Power Supply Rejection Ratio

- mixed-signal circuit IC chip which combines analog and digital devices.

- > Switching activity in digital portion results in ripple within power supplies.

- This ripple may affect op amp output.

- power-supply rejection ratio the ability of a circuit to eliminate any ripple in the circuit power supplies.

- PSRR is generally improved through utilization of capacitors.

(eq12.42)  $PSRR^{+} \equiv A_{d} / A^{+}$ (eq12.43)  $PSRR^{-} \equiv A_{d} / A^{-}$  $(eq12.44) A^+ \equiv V_o / V_{dd}$  $(eq12.45) A^{-} \equiv V_{o} / V_{ss}$ (eq12.46)  $V_o = V_{ss} \frac{I_{o7}}{I_{o6} + I_{o7}}$ (eq12.47)  $A^- \equiv V_o / V_{ss} = \frac{r_{o7}}{r_{o6} + r_{o7}}$ (eq12.48)  $PSRR^{-} \equiv A_d / A^{-} = g_{m1} (r_{o2} | | r_{o4}) g_{m6} r_{o6}$

# 12.1.8. Design Trade-Offs

- The performance of the two-stage CMOS amplifier are primarily determined by two design parameters:

- Length (L) of channel of each MOSFET

- > Overdrive voltage ( $V_{OV}$ ) at which transistor is operated.

- **transition frequency**  $(f_T)$  is defined below. It determined high-frequency operation.

(eq12.49)

$$f_T = g_m / [2\pi (C_{gs} + C_{gd})]$$

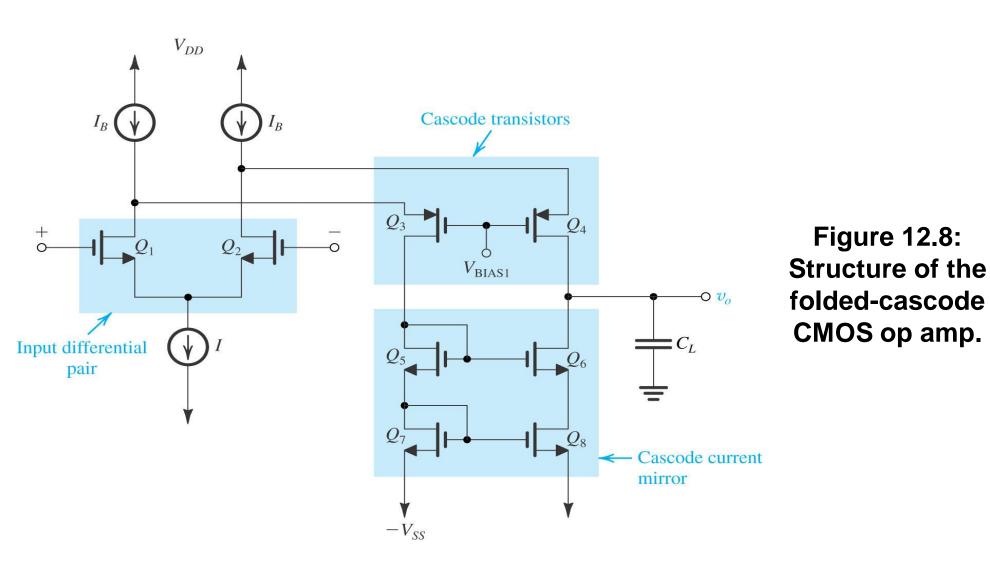

# 12.2. The Folded-Cascode CMOS Op Amp

Figure 12.9: A more complete circuit for the folded-cascode CMOS amplifier of Fig. 12.8.

#### 12.2.2. Input Common-Mode Range and Output Swing

$$\begin{array}{l} (\text{eq12.51}) \ V_{ICMmax} = V_{DD} - \left| V_{OV9} \right| + V_{tn} \\ (\text{eq12.52}) \ V_{ICMmin} = -V_{SS} + V_{OV11} + V_{OV1} + V_{tn} \\ (\text{eq12.53}) \ - V_{SS} + V_{OV11} + V_{OV1} + V_{tn} \leq V_{ICM} \leq V_{DD} - \left| V_{OV9} \right| + V_{tn} \\ (\text{eq12.54}) \ V_{BIAS} = V_{DD} - \left| V_{OV10} \right| - V_{SG4} \\ (\text{eq12.55}) \ V_{Omax} = V_{DD} - \left| V_{OV10} \right| - \left| V_{OV4} \right| \\ (\text{eq12.56}) \ V_{Omin} = -V_{SS} + V_{OV7} + V_{OV5} + V_{tn} \end{array}$$

## 12.2.3. Voltage Gain

$$(eq12.57) G_{m} = g_{m1} = g_{m2}$$

$$(eq12.58) G_{m} = \frac{2(1/2)}{V_{OV1}} = \frac{1}{V_{OV1}}$$

$$(eq12.59) R_{o} = R_{o4} || R_{o6}$$

$$(eq12.60) R_{o4} = g_{m4}r_{o4} (r_{o2} || r_{o10})$$

$$(eq12.61) R_{o6} = g_{m6}r_{o6}r_{o8}$$

$$(eq12.62) R_{o} = \left[g_{m4}r_{o4} (r_{o2} || r_{o10})\right] || \left[g_{m6}r_{o6}r_{o8}\right]$$

$$(eq12.63) A_{v} = G_{m}R_{o}$$

Figure 12.10: Small-signal equivalent circuit of the folded-cascode CMOS amplifier. Note that this circuit is in effect an operational transconductance amplifier (OTA)

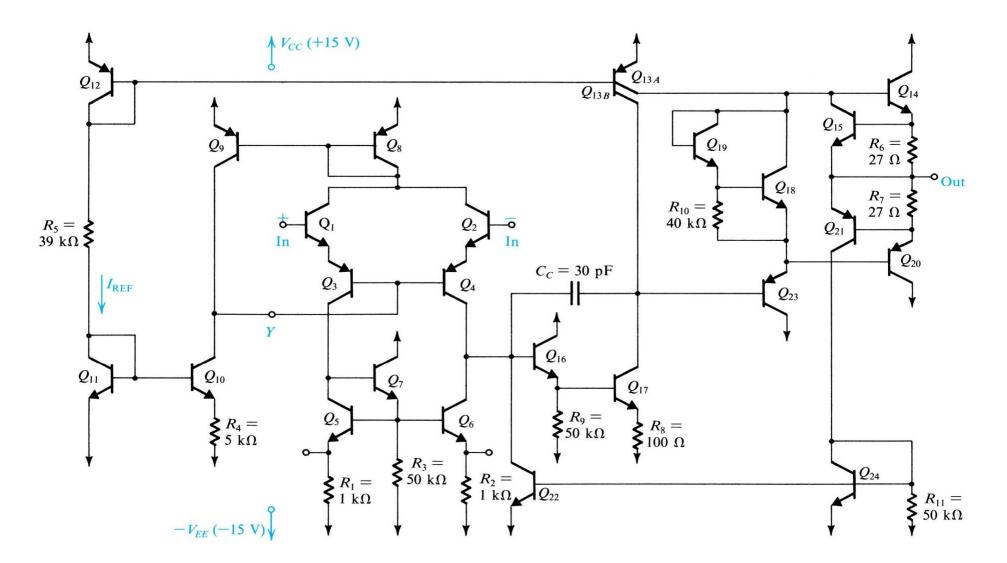

# 12.3. The 741 Op-Amp Circuit

- Sections 12.3. through 12.6 focus on the 741 op-amp circuit.

- Figure 12.13. provides a circuit schematic.

- > The design uses many transistors, few resistors.

- 741 requires two power supplies.

- $V_{CC} = V_{EE} = 15 V$

Figure 12.13: The 741 op-amp circuit: Q11, Q12, and R5 generate a reference bias current; *I*REF. Q10, Q9, and Q8 bias the input stage, which is composed of Q1 to Q7. The second gain stage is composed of Q16 and Q17 with Q13B acting as active load. The class AB output stage is formed by Q14 and Q20 with biasing devices Q13A, Q18, and Q19, and an input buffer Q23. Transistors Q15, Q21, Q24, and Q22 serve to protect the amplifier against output short circuits and are normally cut off.

# 12.3.3. The Input Stage

- 741 consists of three-stages:

- > Input Differential Stage ( $Q_1$  through  $Q_7$ )

- Emitter Followers: Q<sub>1</sub>, Q<sub>2</sub>

- Differential Common-Base: Q<sub>3</sub>, Q<sub>4</sub>

- Load Circuit: Q<sub>5</sub>, Q<sub>6</sub>, Q<sub>7</sub>

- Biasing: Q<sub>8</sub>, Q<sub>9</sub>, Q<sub>10</sub>

- Intermediate Single-Ended High-Gain Stage

- Output-Buffering Stage (other transistors)

# 12.3.4. The Second Stage

- Consists of Q<sub>16</sub>, Q<sub>17</sub>, and Q<sub>13B</sub>

- ➤ Emitter Follower: Q<sub>16</sub>

- ➢ Common-Emitter: Q<sub>17</sub>

- ➤ Load: Q<sub>13B</sub>

- Output of second stage is taken at collector of  $Q_{17}$ .

- Capacitor  $C_c$  is connected in feedback path of second stage.

- Frequency compensation using Miller Technique.

# 12.3.5. The Output Stage

- Provides low output resistance.

- Able to supply relatively large load current.

> With minimal power dissipation.

- Consists of  $Q_{14}$  and  $Q_{20}$ .

- Complementary pair.

- Transistors  $Q_{18}$  and  $Q_{19}$  are fed by current source  $Q_{13A}$  and bias transistors  $Q_{14}$  and  $Q_{20}$ .

#### 12.3.6. Device Parameters

- **npn:**  $I_{\rm S} = 10^{-14} A$ ,  $\beta = 200$ ,  $V_{\rm A} = 125 V$

- **pnp:**  $I_{\rm S} = 10^{-14} A$ ,  $\beta = 50$ ,  $V_{\rm A} = 50 V$

- Q<sub>13A</sub> and Q<sub>13B</sub>: I<sub>SA</sub> = 0.25(10<sup>-14</sup>)A, I<sub>SB</sub> = 0.75(10<sup>-14</sup>)A

≻ These devices are non-standard.

- Q<sub>14</sub> and Q<sub>20</sub> will be assumed to have area three times of the standard device for increased loading.

#### 12.4. DC Analysis of the 741

for

$$V_{CC} = V_{EE} = 15V$$

,  $V_{EB11} = V_{BE12} = 0.7V$ ,  $I_{REF} = 0.73mA$

$I_{REF} = \frac{V_{CC} - V_{EB12} - V_{BE11} + V_{EE}}{R_5}$

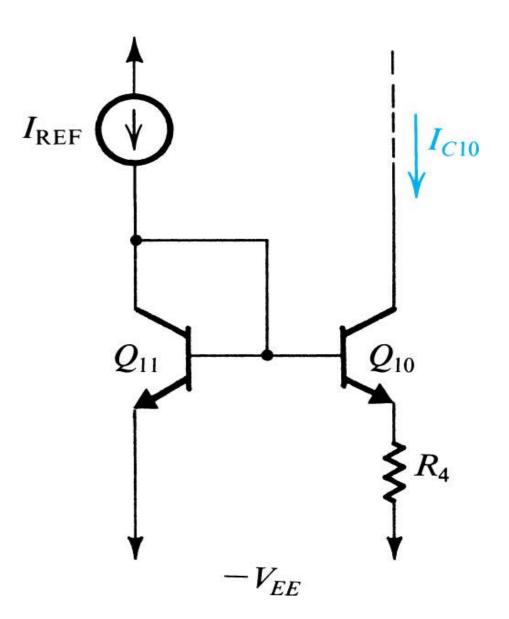

(eq12.75)  $V_T \ln \left(\frac{I_{REF}}{I_{C10}}\right) = I_{C10}R_4$

(eq12.76)  $I_{C5} = I_{C6}$

(eq12.77)  $I_{C5} \approx I_{C3} \approx I$

(eq12.78)  $I_{C6} \approx I_{C4} \approx I$

(eq12.79)  $I_{C7} \approx I_{E7} = \frac{2I}{\beta_N} + \frac{V_{BE6} + IR_2}{R_3}$

Figure 12.14: The Widlar current source that biases the input stage.

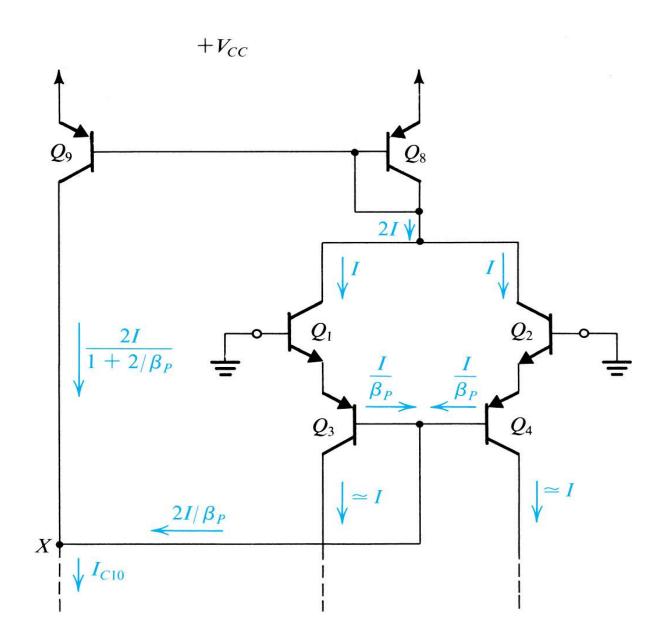

Figure 12.15: The dc analysis of the 741 input stage.

Figure 12.16: The dc analysis of the 741 input stage, continued.

#### 12.4. DC Analysis of the 741

| 2  | 9.5 | $Q_{\rm s}$ | 19  | $Q_{13B}$          | 550  | $Q_{19}$ | 15.8 |

|----|-----|-------------|-----|--------------------|------|----------|------|

| 2  | 9.5 | $Q_9$       | 19  | $Q_{14}$           | 154  | $Q_{20}$ | 154  |

| 2, | 9.5 | $Q_{10}$    | 19  | $Q_{15}$           | 0    | $Q_{21}$ | 0    |

| 24 | 9.5 | $Q_{\rm u}$ | 730 | $Q_{16}$           | 16.2 | $Q_{22}$ | 0    |

| 5  | 9.5 | $Q_{12}$    | 730 | Q17                | 550  | $Q_{23}$ | 180  |

| 26 | 9.5 | $Q_{13,4}$  | 180 | $\mathcal{Q}_{18}$ | 165  | $Q_{24}$ | 0    |

# 12.5. Small Signal Analysis of 741

- One may use small-signal analysis (as in previous chapters) to analyze linear behavior of the 741.

- ➤ Figures 12.18 12.21 describe this process for input stage.

- ➢ Figures 12.25 12.27 describe this process for gain stage.

- ➢ Figures 12.28 12.30 describe this process for output stage.

## 12.5. Small Signal Analysis of 741

Figure 12.21: Small-signal equivalent circuit for the input stage of the 741 op amp.

#### 12.5. Small Signal Analysis of 741

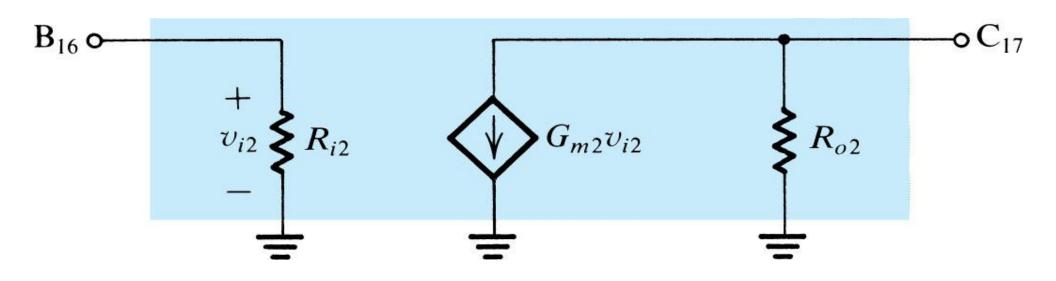

Figure 12.25: Small-signal equivalent-circuit model of the second stage.

- Most CMOS op-amps are designed to operate as part of a VLSI circuit and thus required to drive only small capacitive loads.

Therefore, most do not have a low-output-resistance stage.

- There are basically two approaches to the design of CMOS opamps: a two-stage configuration and a single-stage topology using the folded-cascode circuit.

- In the two-stage CMOS op-amp, approximately equal gains are realized in the two stages.

- The threshold mismatch together with the low transconductance of the input stage result in a larger input offset voltage for the CMOS op-amps than for bipolar units.

- Miller compensation is employed in the two-stage CMOS opamp, but a series resistor is required to place the transmission zero at either s = infinity or on the negative real axis.

- CMOS op-amps have better slew rates (than alt's).

- Use of the cascode configuration increases the gain of a CMOS amplifier stage by about two orders of magnitude, thus making possible a single-stage op-amp.

- The dominant pole of the folded-cascode op-amp is determined by the total capacitance at the output CL. Increasing CL improves the phase margin at the expense of reducing bandwidth.

- By using two complementary input differential pairs in parallel, the common-mode range may be extended.

- The output voltage swing of the folded-cascode op-amp may be extended by utilizing a wide-swing current mirror in place of the cascode mirror.

- The internal circuit of the 741 op-amp embodies many of the design techniques employed in bipolar analog integrated circuits.

- The 741 circuit consists of an input differential stage, a highgain single-ended second stage, and a class AB output stage. It is the basis for many other devices.

- To obtain low input offset voltage and current, and high CMRR, the 741 input stage is designed to be perfectly balanced. The CMRR is increased by common-mode feedback, which also stabilizes the dc operating point.

- To obtain high input resistance and low input bias current, the input stage of the 741 is operated as a very low current level.

- The use of Miller Frequency compensation in the 741 circuit enables locating the dominant pole at a very low frequency, while utilizing a relatively small compensating capacitance.

- Two-stage op-amps may be modeled as a transconductance amplifier feeding an ideal integrator with  $C_C$  as the integrating capacitor.

- The slew rate of a two-stage op-amp is determined by the first-stage bias current and frequency-compensation capacitor.

- While the 741 and similar op-amps nominally operate from 15V power supplies, modern BJT op-amps typically utilize a single ground-referenced supply of only 2 or 3V.

#### **BANDGAP REFERENCES**

# **REFERENCE CIRCUITS**

- A reference circuit is an independent voltage or current source which has a high degree of precision and stability.

- Output voltage/current should be supply.

۲

- Output voltage/current should be

- Output voltage/current should be variations

independent of power

independent of temperature. independent of processing

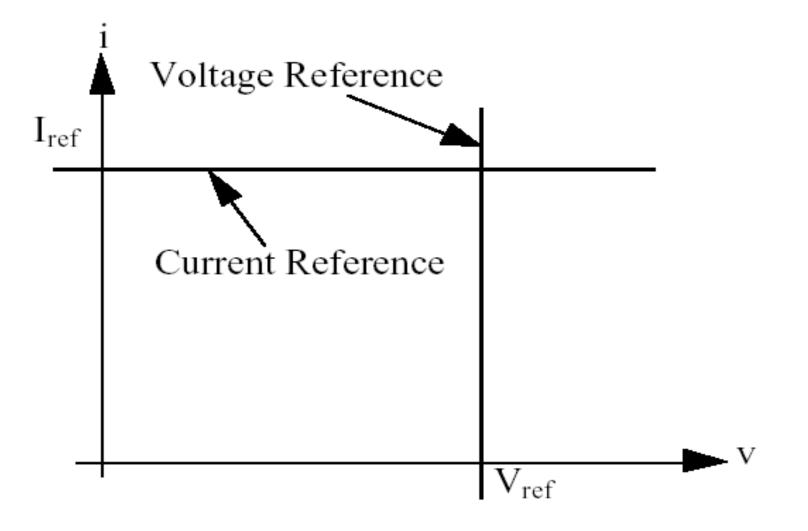

#### I-V curves of ideal references

#### Types of commonly used references

- Voltage dividers passive and active.

- MOS diode reference.

- PN junction diode reference.

- Gate-source threshold reference circuit.

- Base-emitter reference circuit.

- Thermo voltage reference circuit

- Bandgap reference circuit

# Typical variations affecting the references

- Power supply variation (main concern here)

- Load variation ( $r_0 = \infty$  for I-ref,  $r_0 = 0$  for V-ref)

- Temperature variation (main concern also)

- Processes variation (good process and layout)

- Interferences and noise (not considered here)

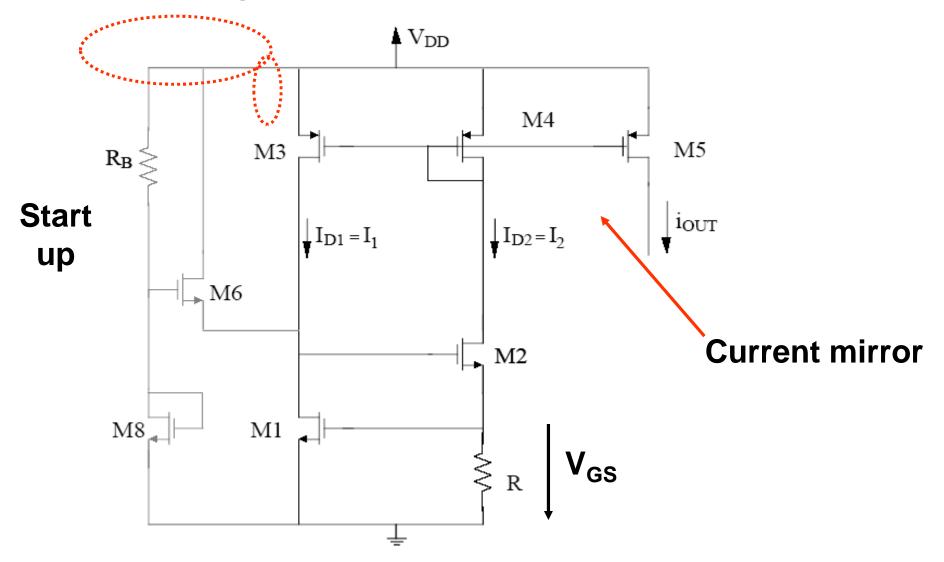

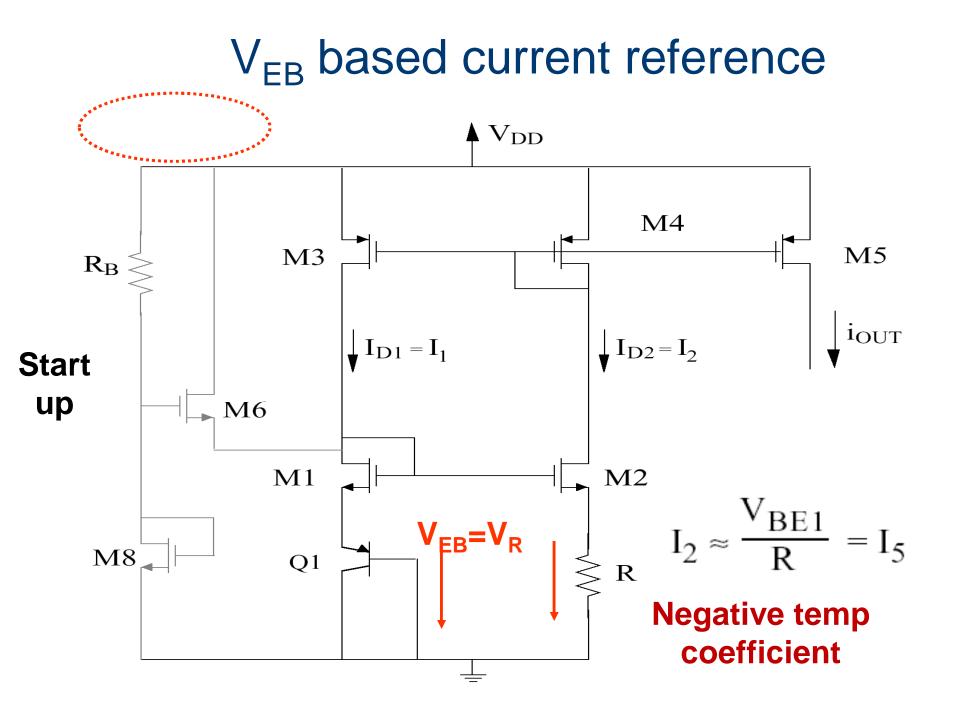

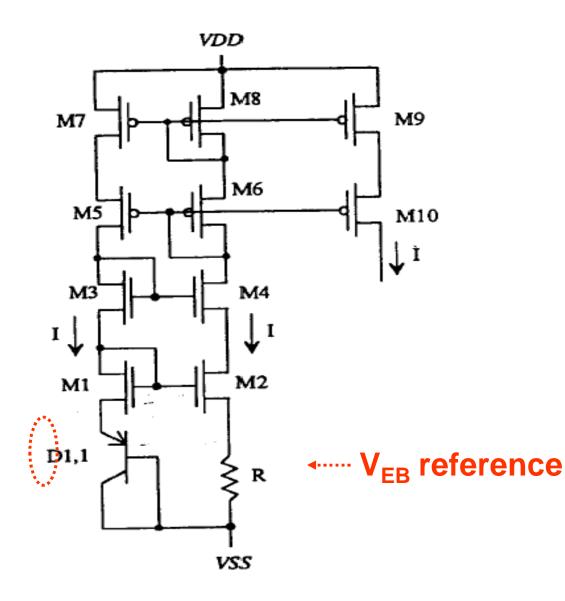

#### $V_{GS}$ based Current reference MOS version: use $V_{GS}$ to generate a current and then use negative feed back stabilize i in MOS

# A cascoded version to increase r<sub>o</sub> and reduce sensitivity:

**Requires start up**

Not shown here

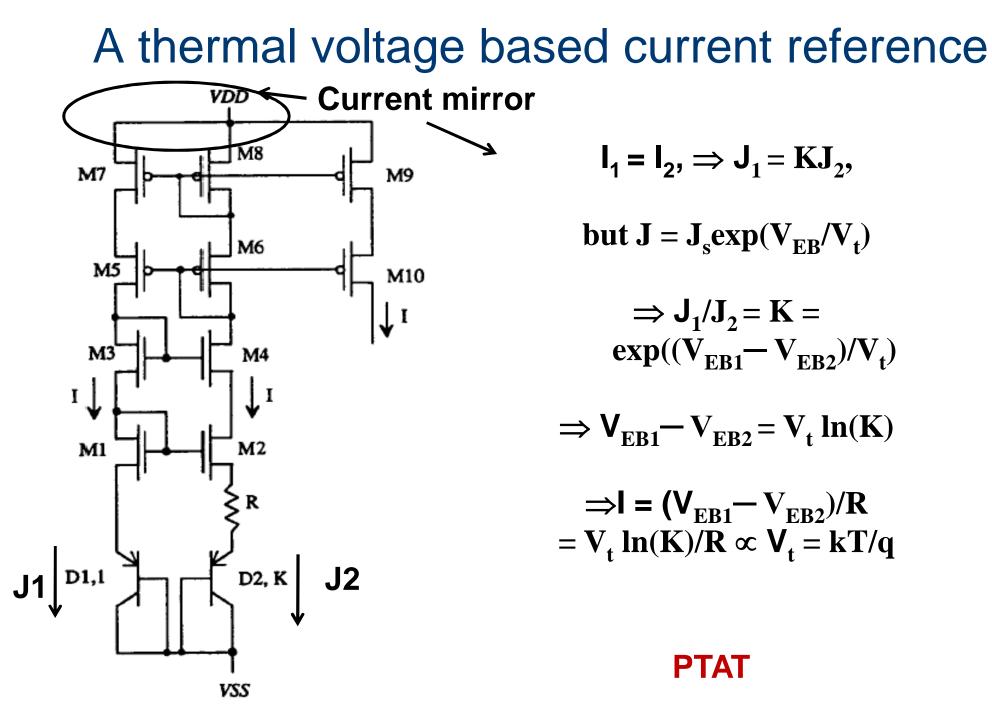

$\mathbf{I}_1 = \mathbf{I}_2, \Rightarrow \mathbf{J}_1 = \mathbf{K}\mathbf{J}_2,$

but

$$J = J_s exp(V_{EB}/V_t)$$

$$\Rightarrow \mathbf{J}_1 / \mathbf{J}_2 = \mathbf{K} = \\ \exp((\mathbf{V}_{\text{EB1}} - \mathbf{V}_{\text{EB2}}) / \mathbf{V}_t)$$

$$\Rightarrow \mathsf{V}_{\text{EB1}} - \mathsf{V}_{\text{EB2}} = \mathsf{V}_{\text{t}} \ln(\mathsf{K})$$

$$\Rightarrow I = (V_{EB1} - V_{EB2})/R$$

$$= V_t \ln(K)/R \propto V_t = kT/q$$

**PTAT**

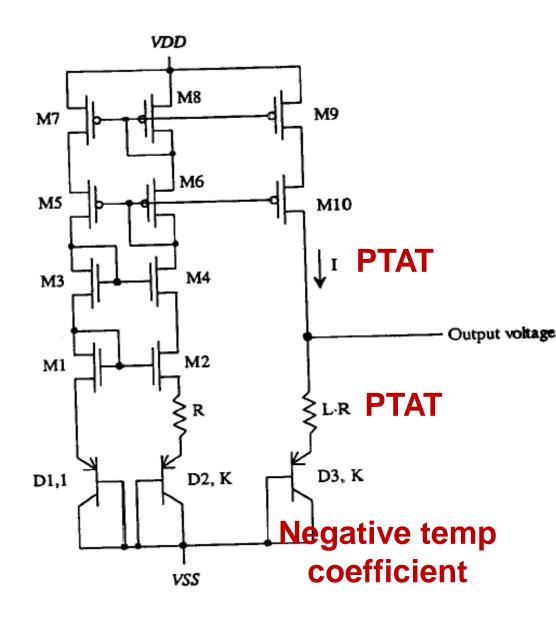

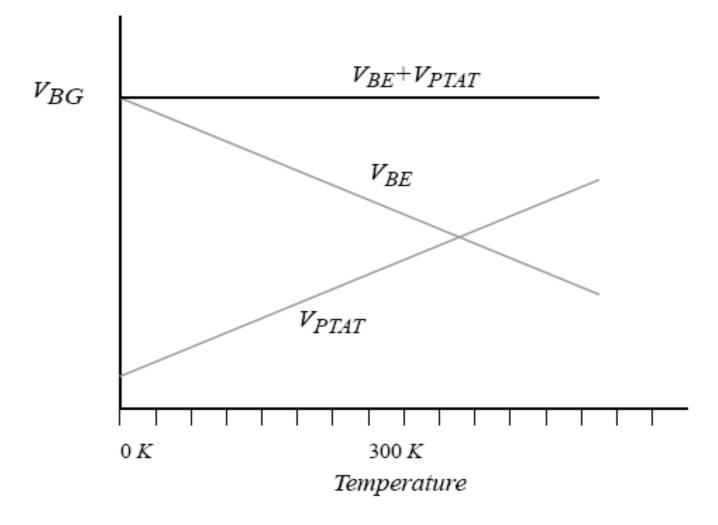

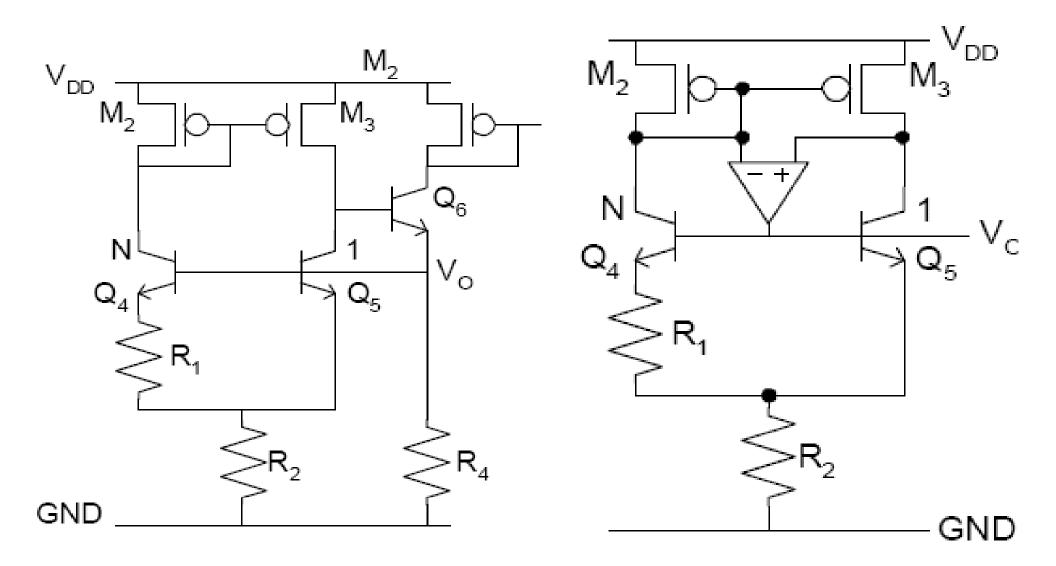

### A band gap voltage reference

$V_{out} = V_{EB3} + I^*L^*R = V_{EB3} + I^*L^*R$ (kT/q)\*Lln(K)  $\partial V_{out} / \partial T = \partial V_{EB3} / \partial T +$ (k/q)\*Lln(K) At room temperature,  $\partial V_{EB3} / \partial T = -2.2 \text{ mV/}{}^{\circ}\text{C},$  $k/q = +0.085 \text{ mV/}^{\circ}\text{C}.$ Hence, choosing appropriate L and K can make  $\partial V_{out} / \partial T = 0$ When this happens,  $V_{out} =$ 1.26 V

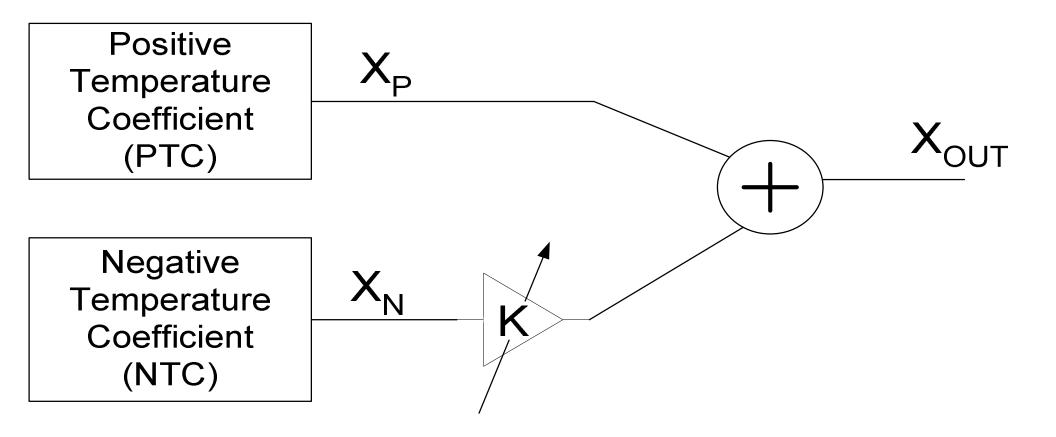

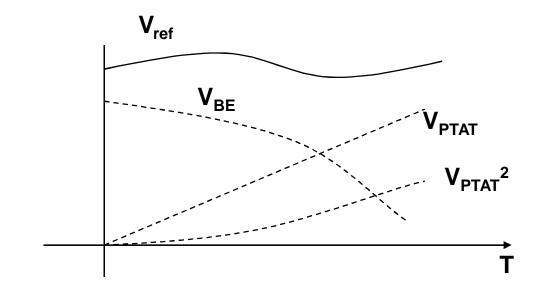

General principle of bandgap reference

Generate a negatively PTAT (Proportional To Absolute Temperature) and a positively PTAT voltages and sum them appropriately.

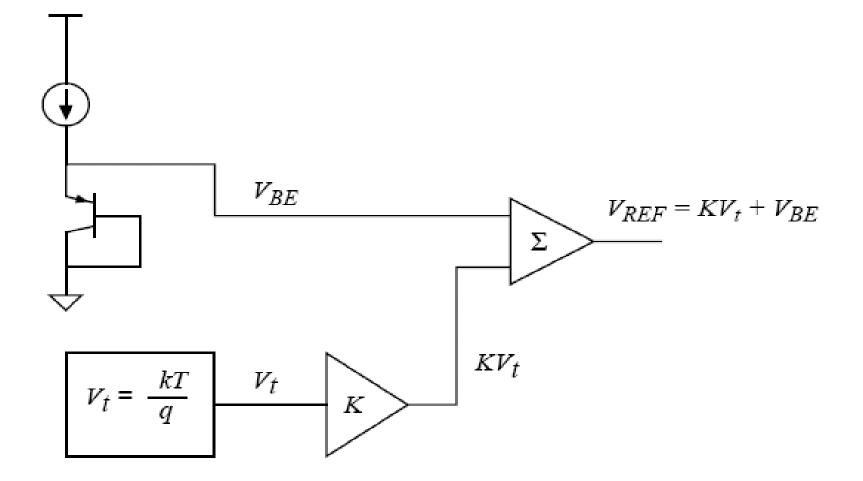

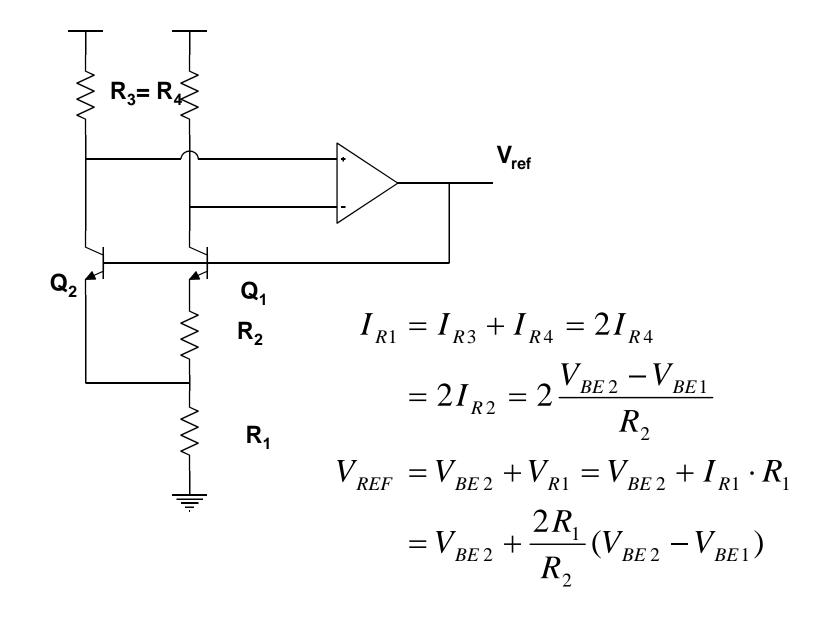

### A Common way of bandgap reference

## *V<sub>BE</sub>* is negatively PTAT at roughly -2.2 mV/°C at room temperature, called CTAT

$V_t$  ( $V_t = kT/q$ ) is PTAT that has a temperature coefficient of +0.085 mV/°C at room temperature.

Multiply  $V_t$  by a constant K and sum it with the  $V_{BE}$  to get

$$V_{\mathsf{REF}} = V_{BE} + KV_t$$

If K is right, temperature coefficient can be zero.

In general, use  $V_{BE} + V_{PTAT}$

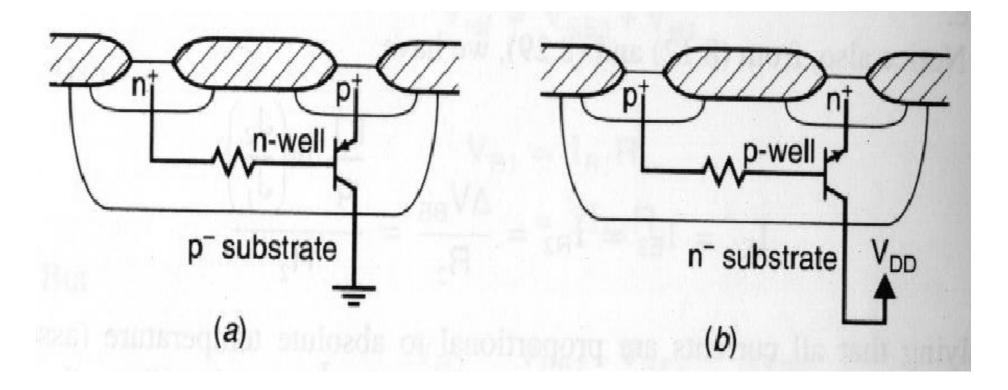

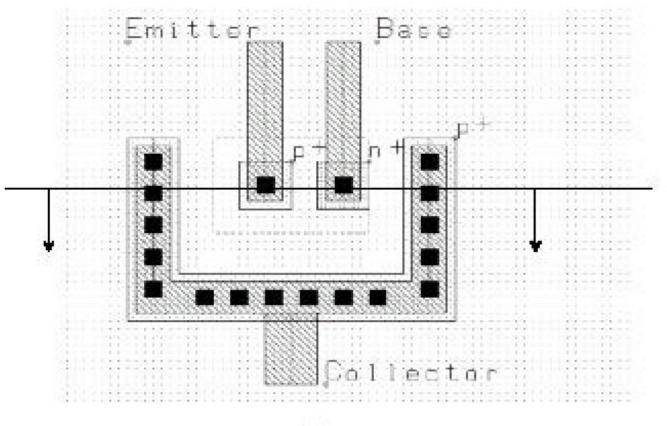

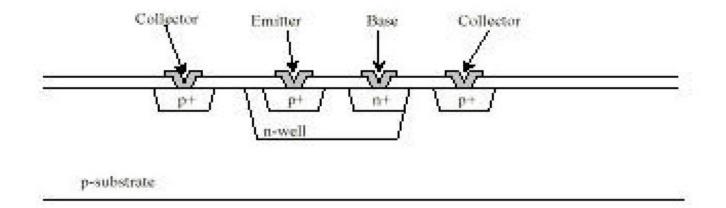

How to get Bipolar in CMOS?

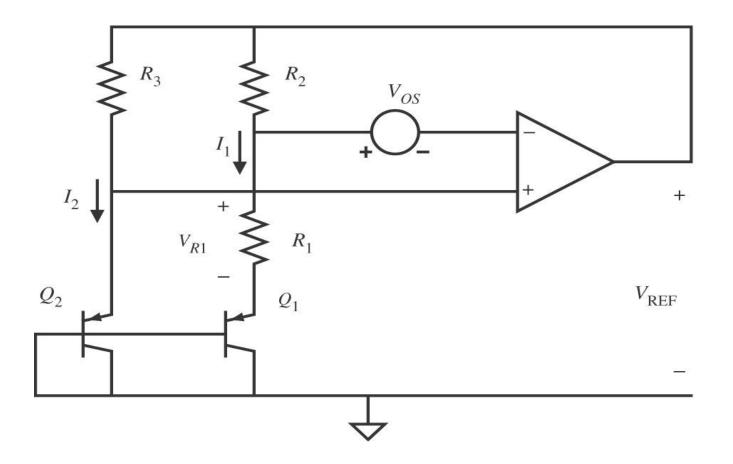

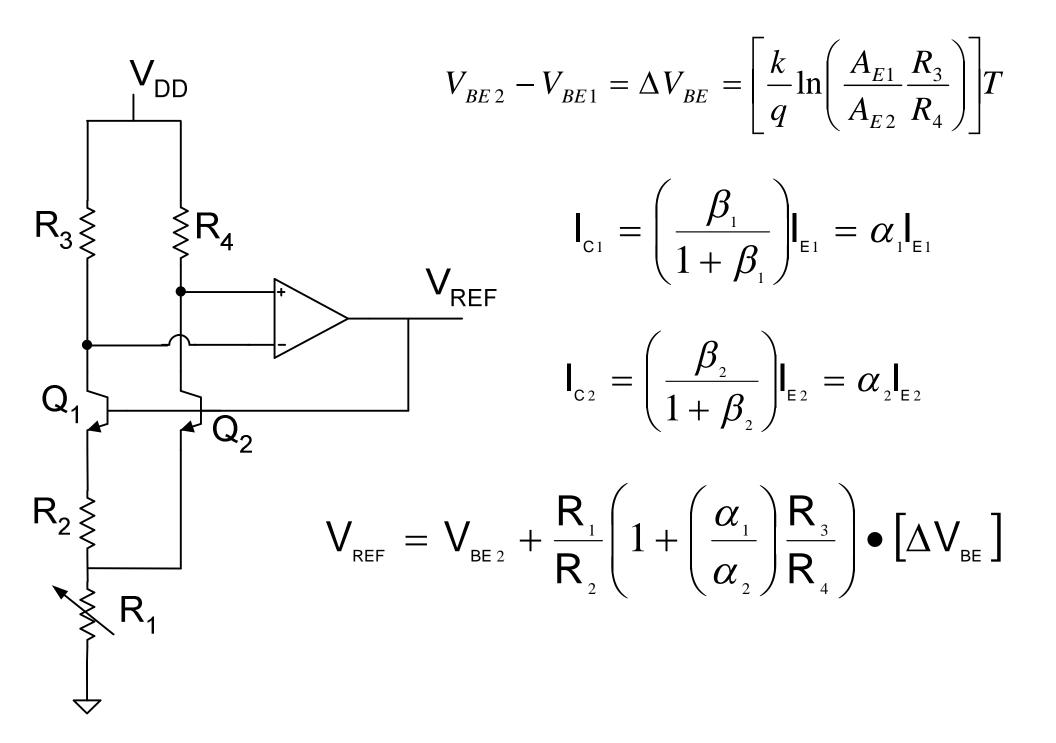

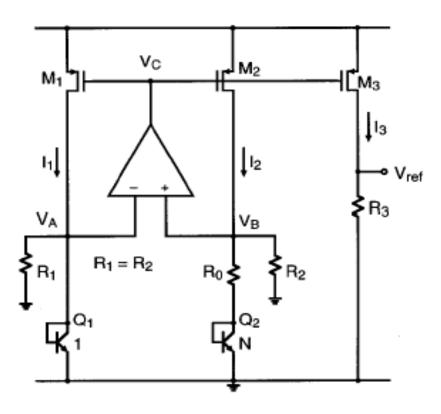

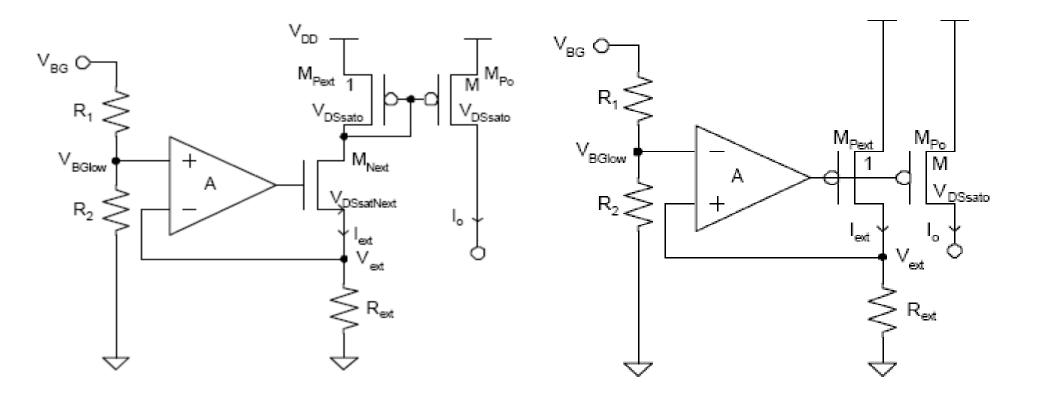

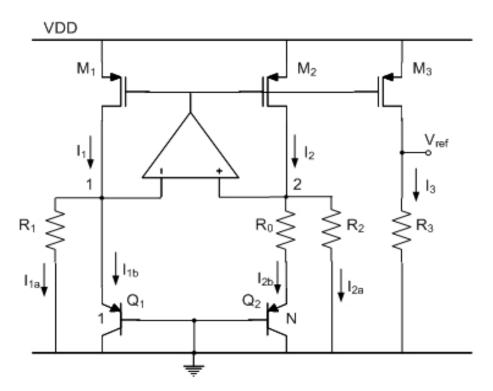

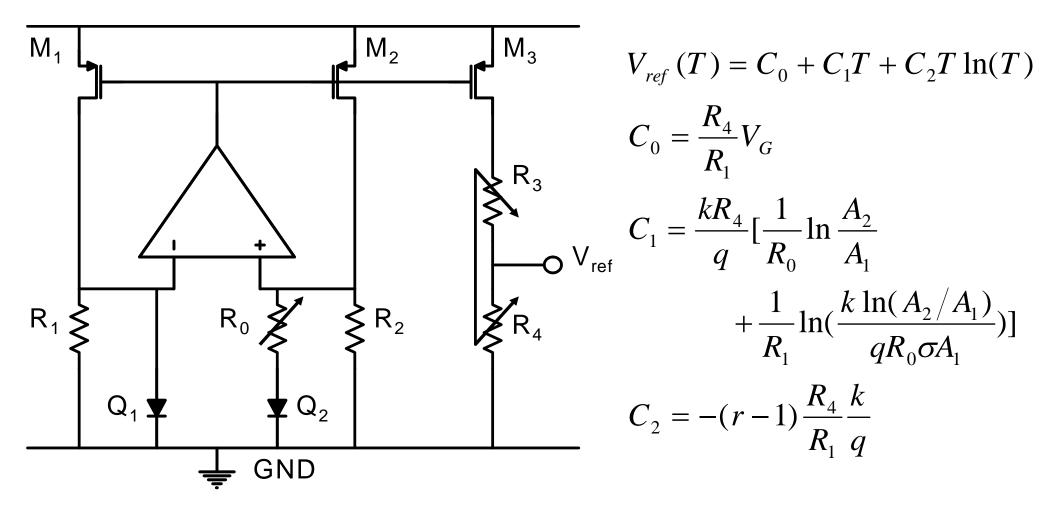

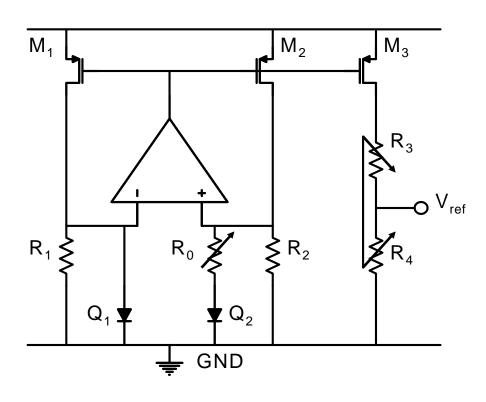

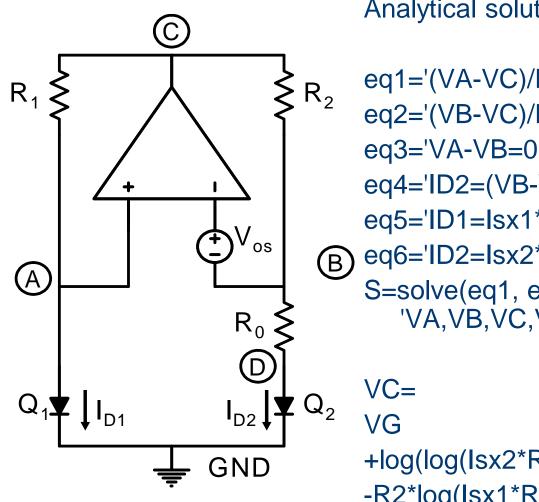

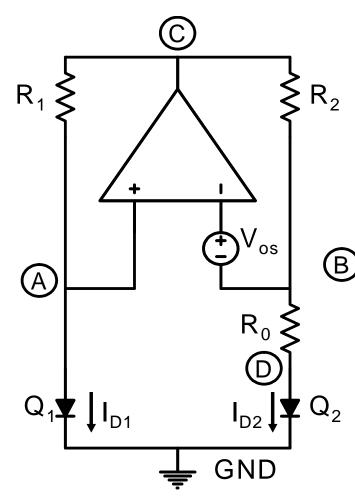

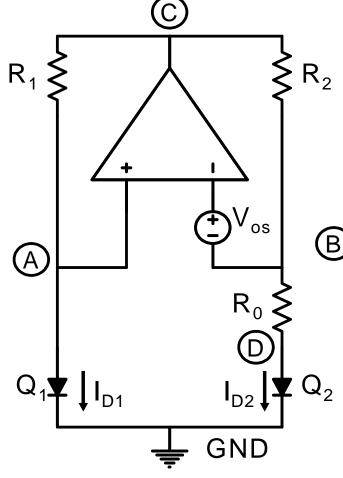

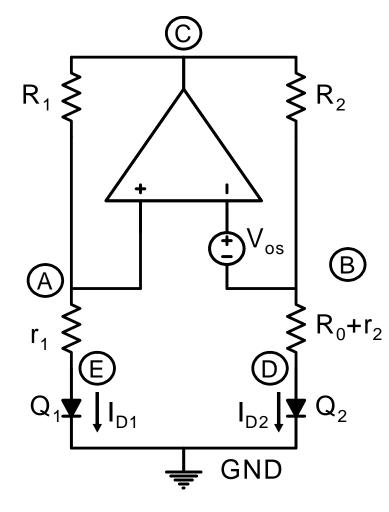

#### A conventional CMOS bandgap reference for a nwell process

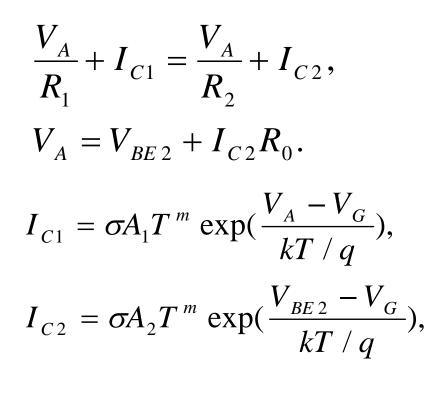

$V_{OS}$  represents input offset voltage of the amplifier. Transistors Q<sub>1</sub> and Q<sub>2</sub> are assumed to have emitter-base areas of  $A_{E1}$  and  $A_{E2}$ , respectively.

If  $V_{OS}$  is zero, then the voltage across  $R_1$  is given as

$$V_{R1} = V_{BE2} - V_{BE1} = V_t \ln\left(\frac{J_2}{J_{S2}}\right) - V_t \ln\left(\frac{J_1}{J_{S1}}\right) = V_t \ln\left(\frac{I_2A_{E1}}{I_1A_{E2}}\right)$$

$$I_1R_2 = I_2R_3 \qquad V_{REF} = V_{BE2} + I_1R_2 = V_{BE2} + V_{R1}\left(\frac{R_2}{R_1}\right)$$

$$V_{\text{REF}} = V_{BE2} + \left(\frac{R_2}{R_1}\right) V_t \ln\left(\frac{R_2 A_{E1}}{R_3 A_{E2}}\right)$$

$$K = \left(\frac{R_2}{R_1}\right) \ln \left(\frac{R_2 A_{E1}}{R_3 A_{E2}}\right)$$

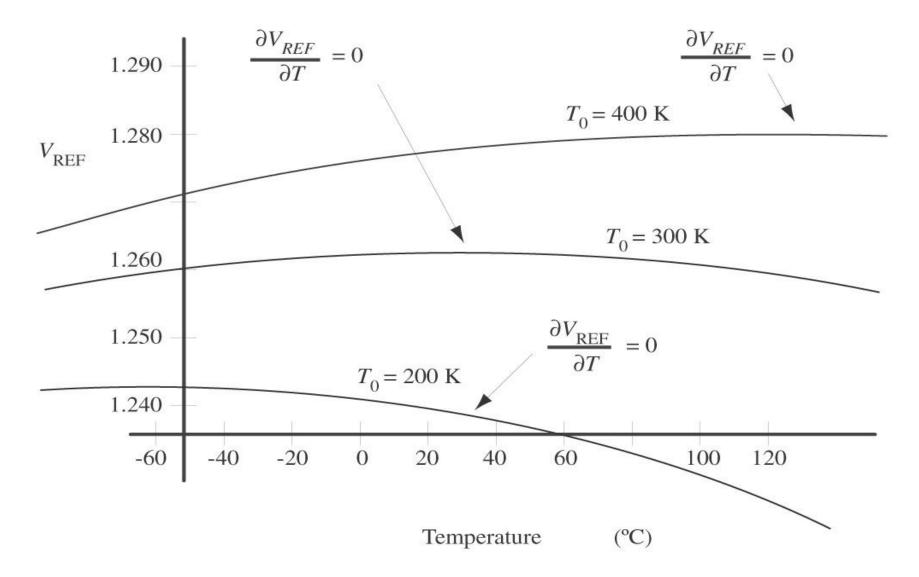

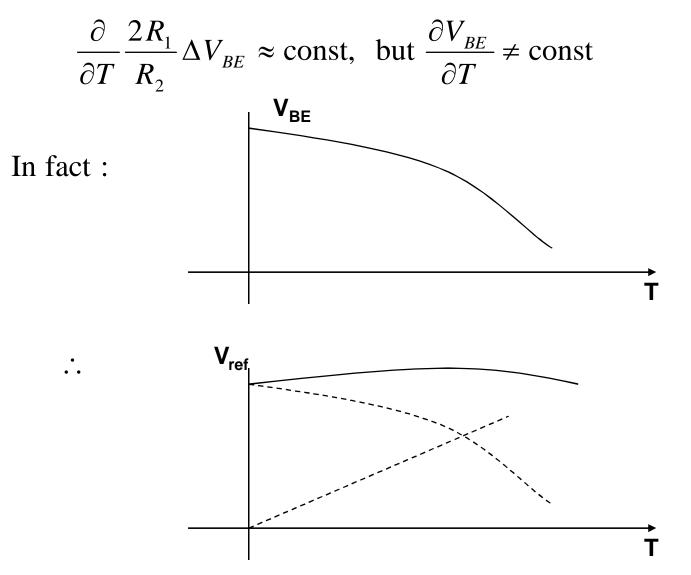

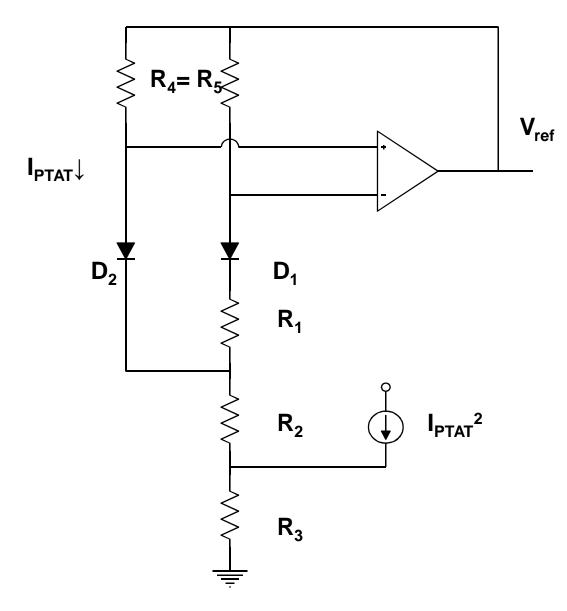

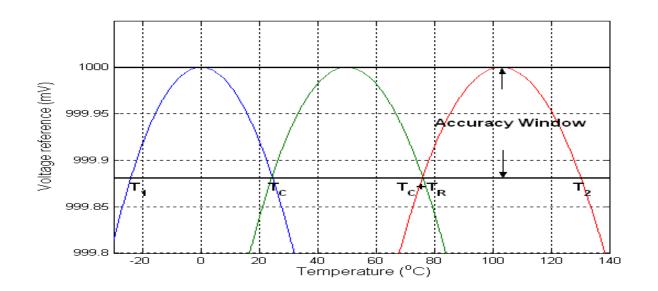

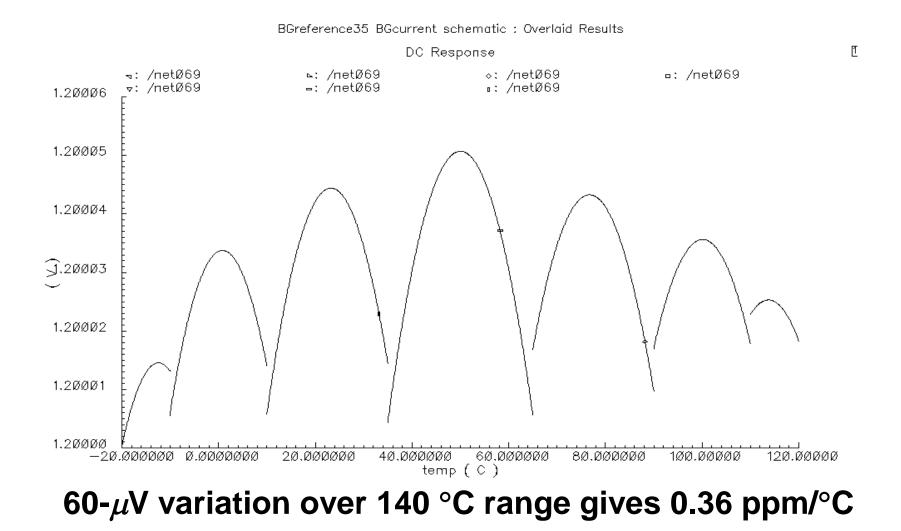

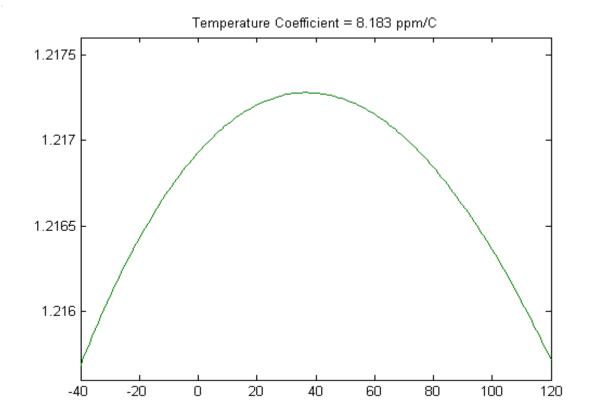

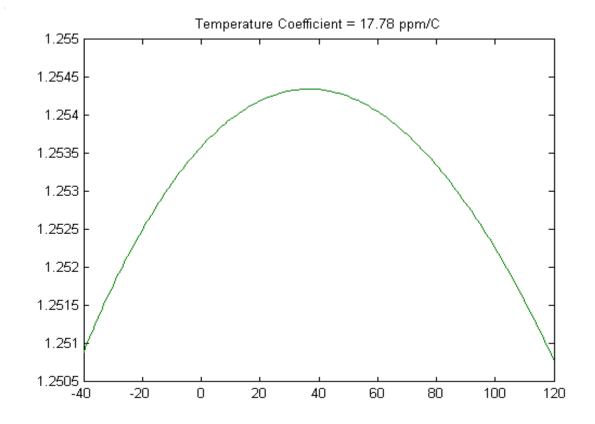

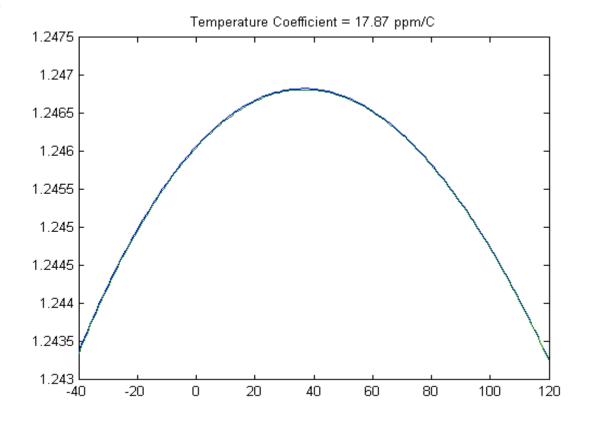

#### Bandgap reference still varies a little with temp

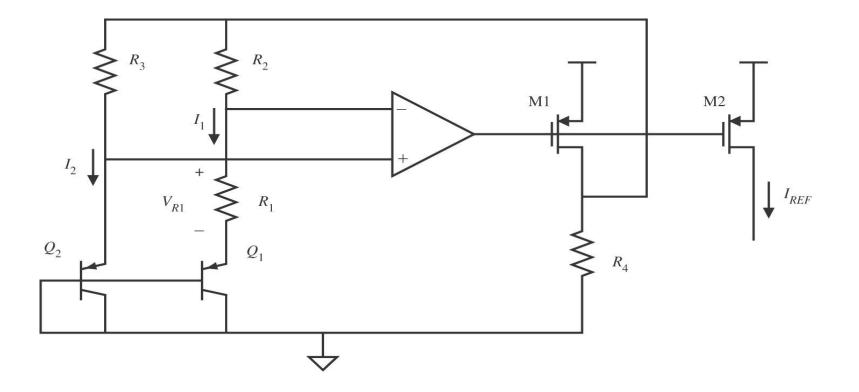

#### Converting a bandgap voltage reference to a current reference

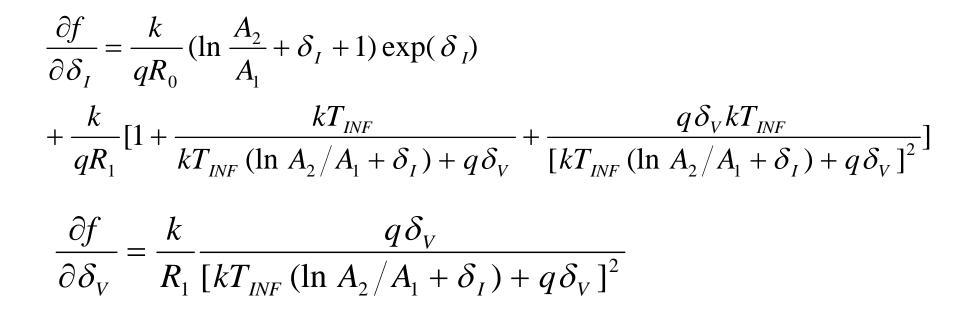

$Vref=I_3^*R_3=$

$$R_{3}\left[\frac{V_{Go}}{R_{1}} + \left(\frac{1}{R_{0}}\frac{k}{q}\ln(\frac{A_{2}}{A_{1}}) + \frac{V_{BE} - V_{G0}}{T_{o}}\right) \cdot T + \frac{m-1}{R_{1}q}kT \cdot \ln(\frac{T_{o}}{T})\right]$$

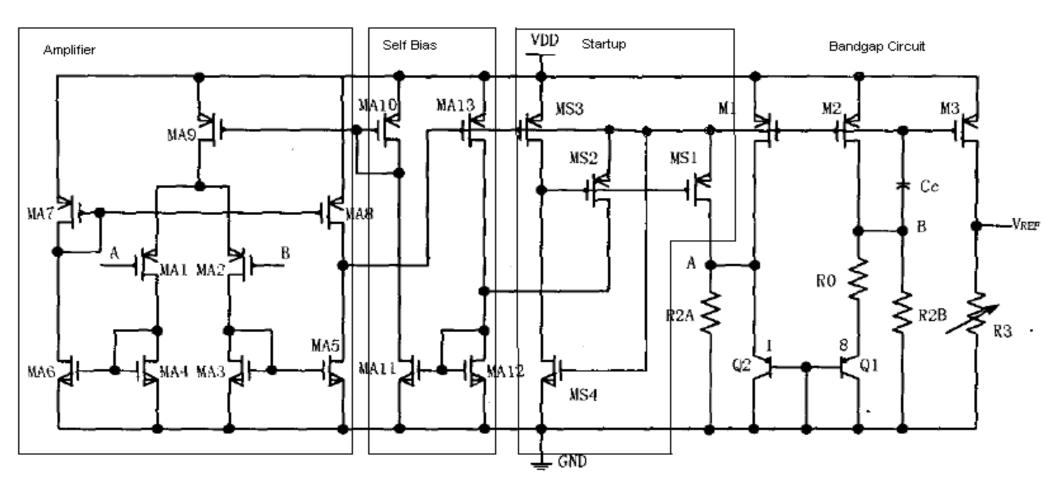

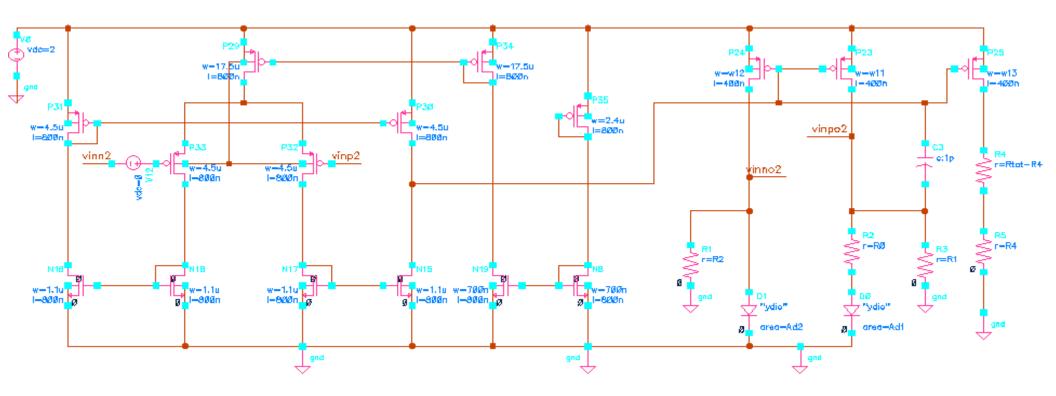

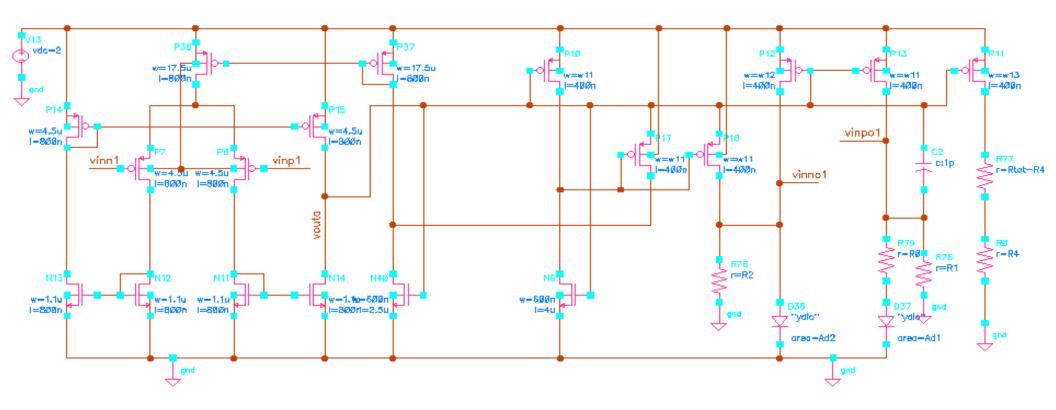

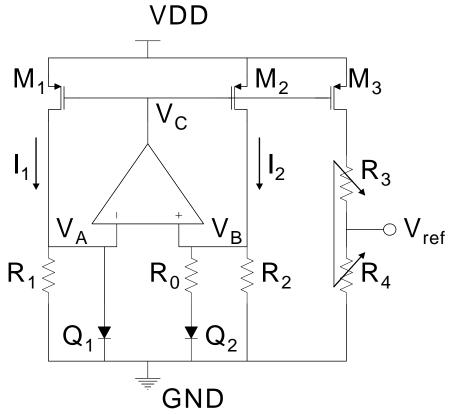

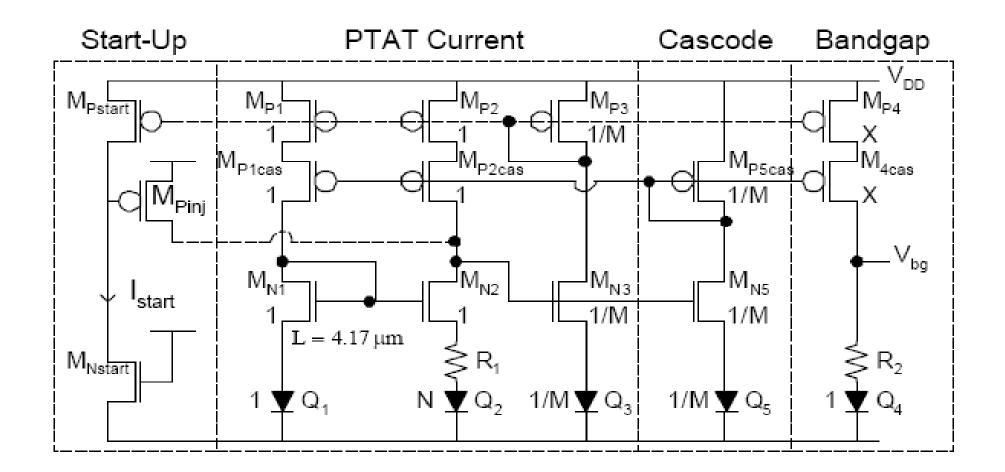

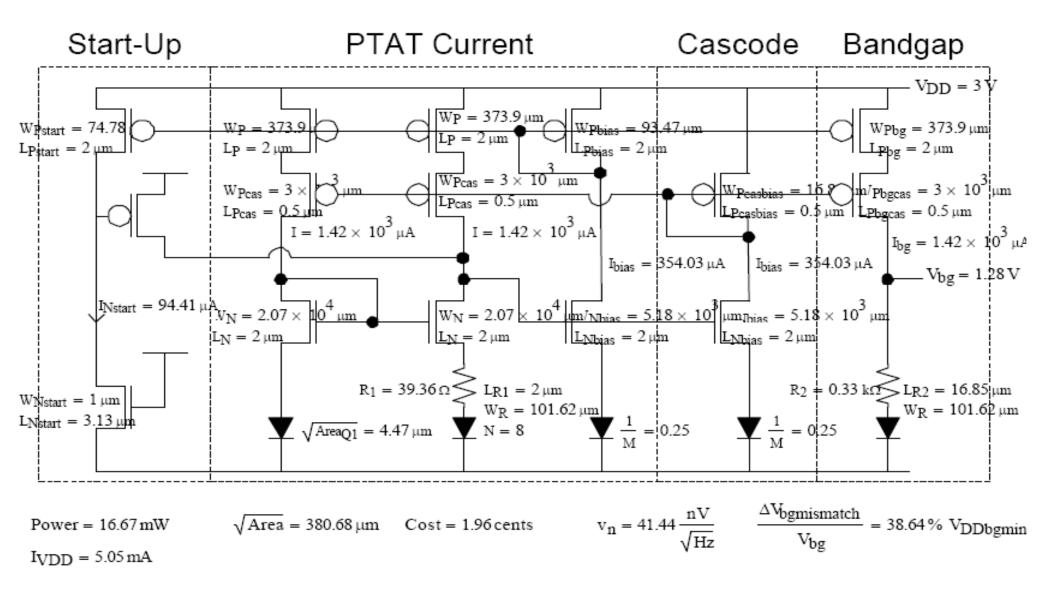

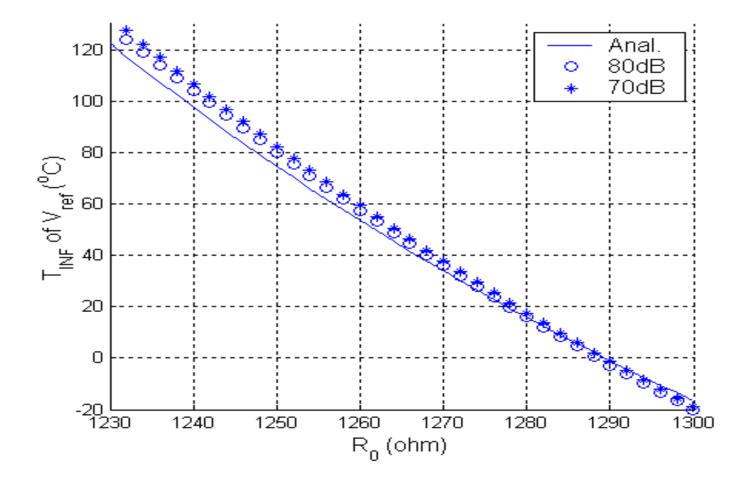

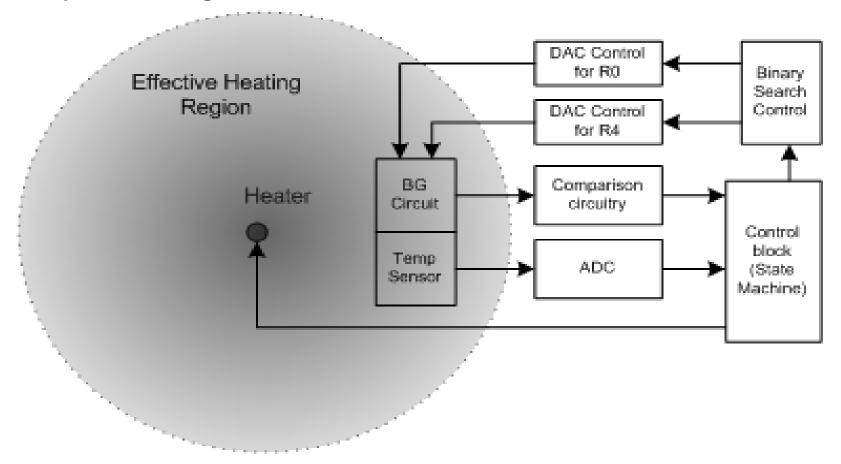

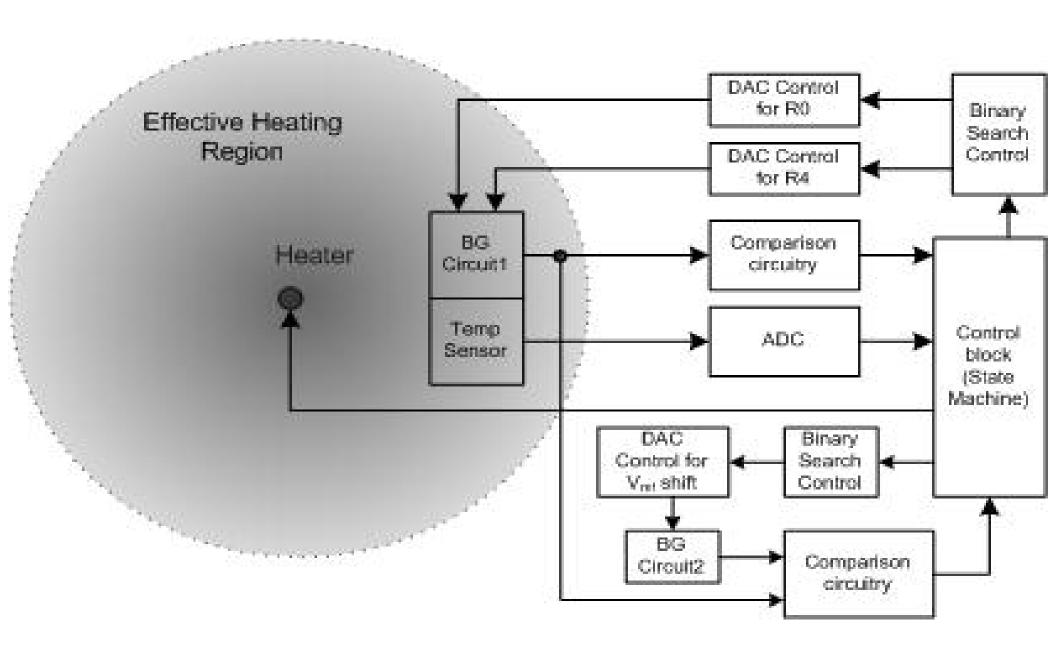

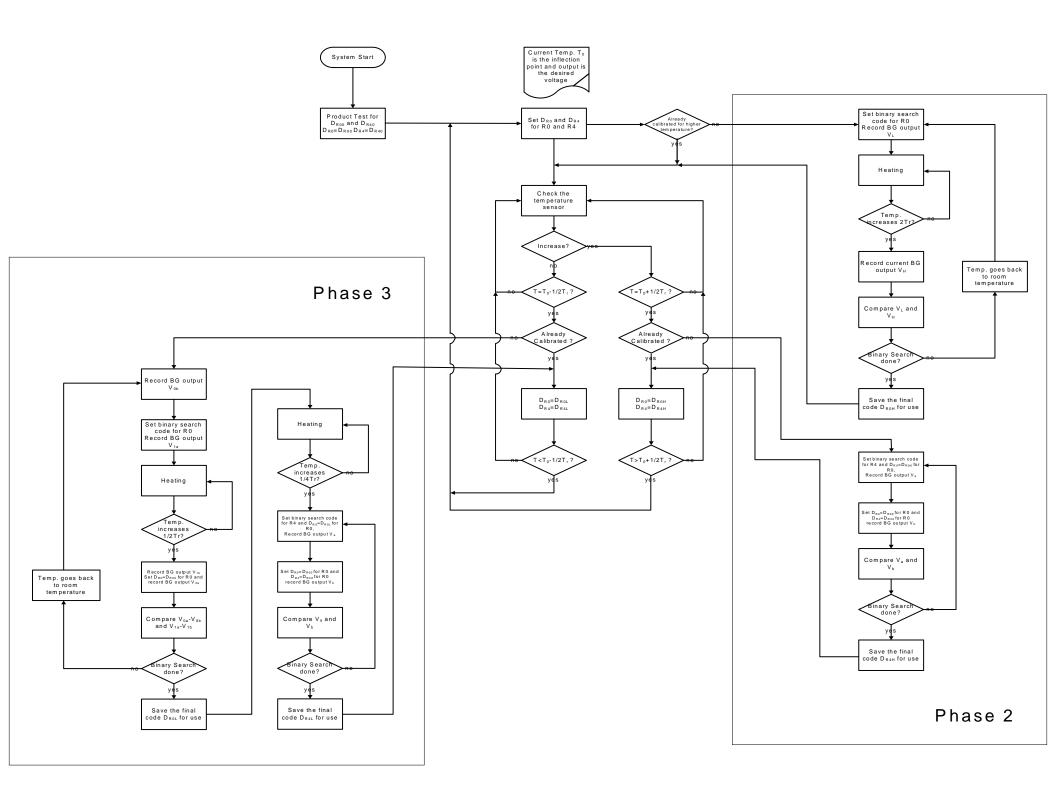

Bandgap circuit formed by transistors M1, M2, M3, Q1, Q2, resistors R0, R2A, R2B, and R3.

Cc is inter-stage compensation capacitor. Think of M2 as the second stage of your two stage amplifier, then Cc is connected between output B and the input Vc.

- **Amplifier:** MA1~MA9, MA9 is the tail current source, MA1 and MA2 consistent of the differential input pair of the op amp, MA3~MA6 form the current mirrors in the amplifier, MA7 converts the amplifier output to single ended, and MA5 and MA8 form the push pull output node.

- ➤ The offset voltage of the amplifier is critical factor, → use large size differential input pair and careful layout; and use current mirror amplifier to reduce systematic offset.

- 2V supple voltage is sufficient to make sure that all the transistors in the amplifier work in saturation.

- PMOS input differential pair is used because the input common mode range (A,B nodes) is changing approximately from 0.8 to 0.6 V and in this case NMOS input pair won't work.

- Self Bias: MA10~MA13, a self-bias approach is used in this circuit to bias the amplifier. Bias voltage for the primary stage current source MA13 is provided by the output of the amplifier, i.e. there forms a self-feedback access from MA8 drain output to bias current source MA9 through current mirror MA10~MA13.

- **Startup Circuit:** MS1~MS4. When the output of the amplifier is close to Vdd, the circuit will not work without the start-up circuit. With the start-up circuit MS1 and MS2 will conduct current into the BG circuit and the amplifier respectively.

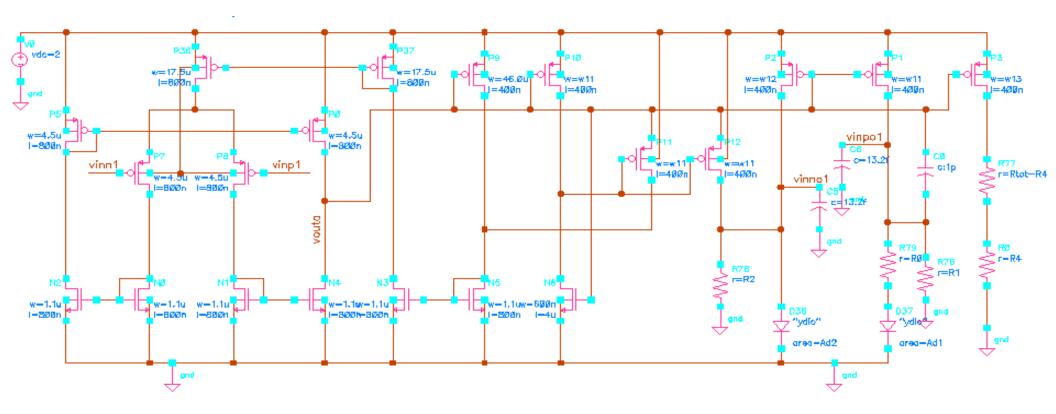

#### Cc is 1 pF

## To have better mirror accuracy, M3 is driving a constant resistor Rtot.

Capacitors at nodes A and B are added.

#### **BG Circuit with simple bias circuit**

No self biasing No startup problem, no startup circuit needed Amplifier current depends on power supply voltage

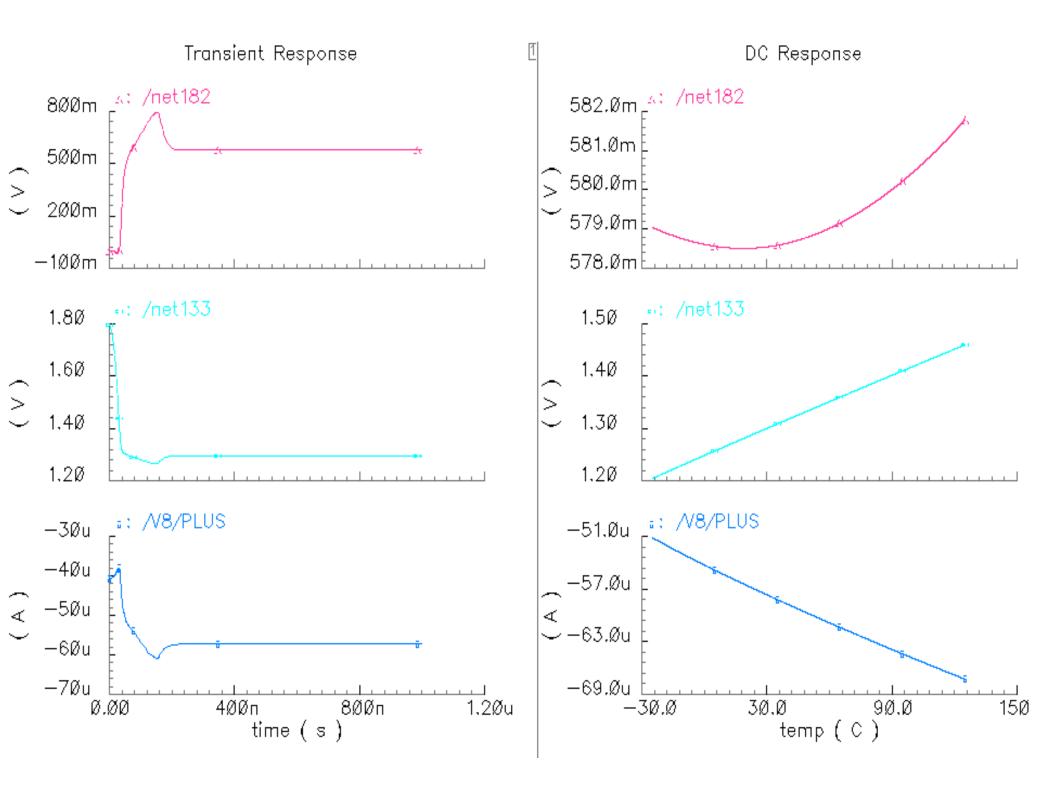

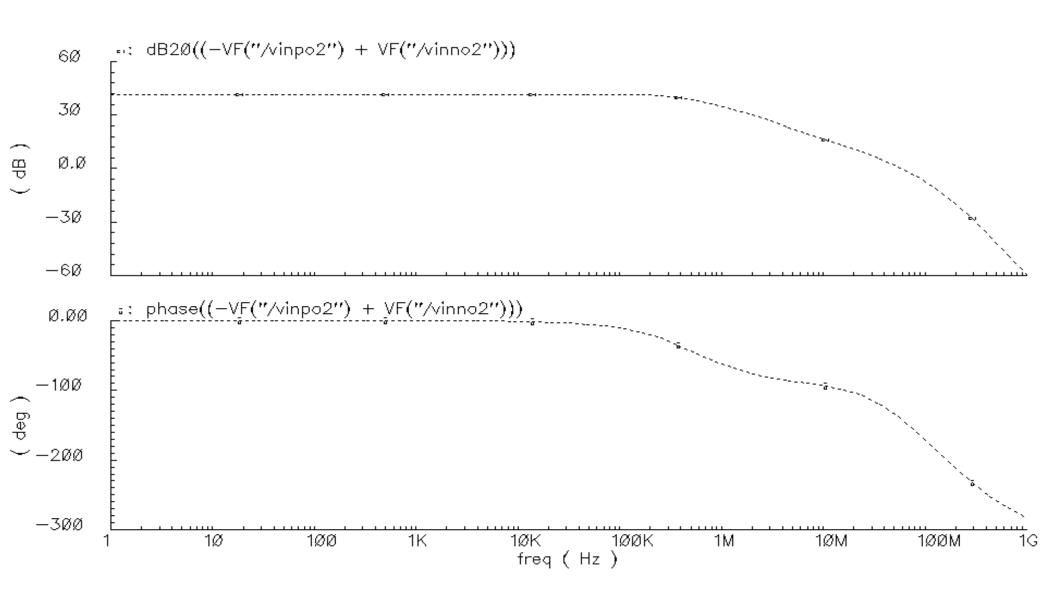

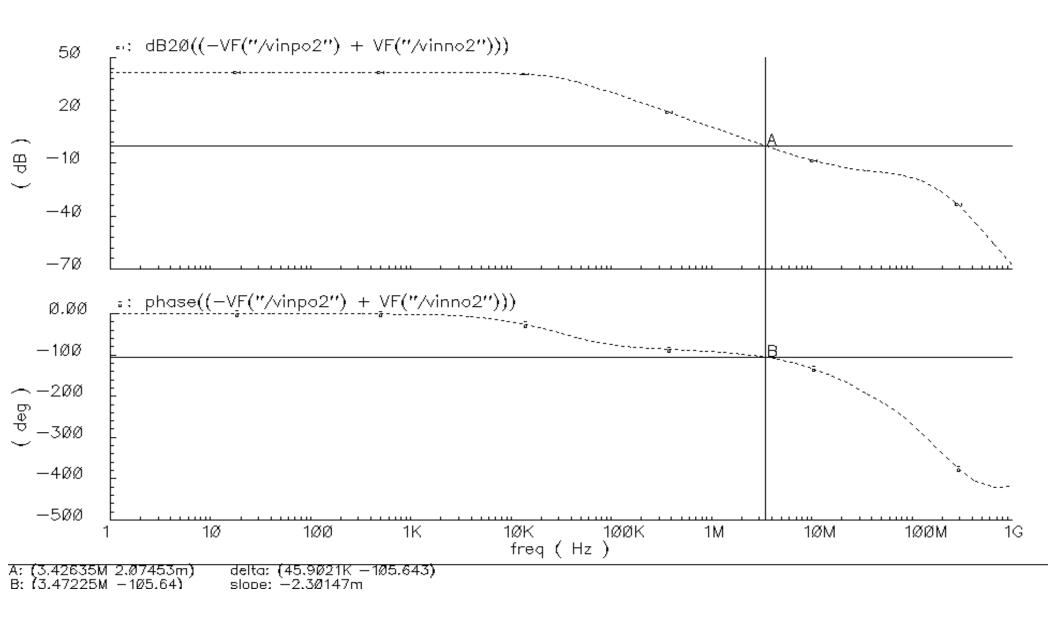

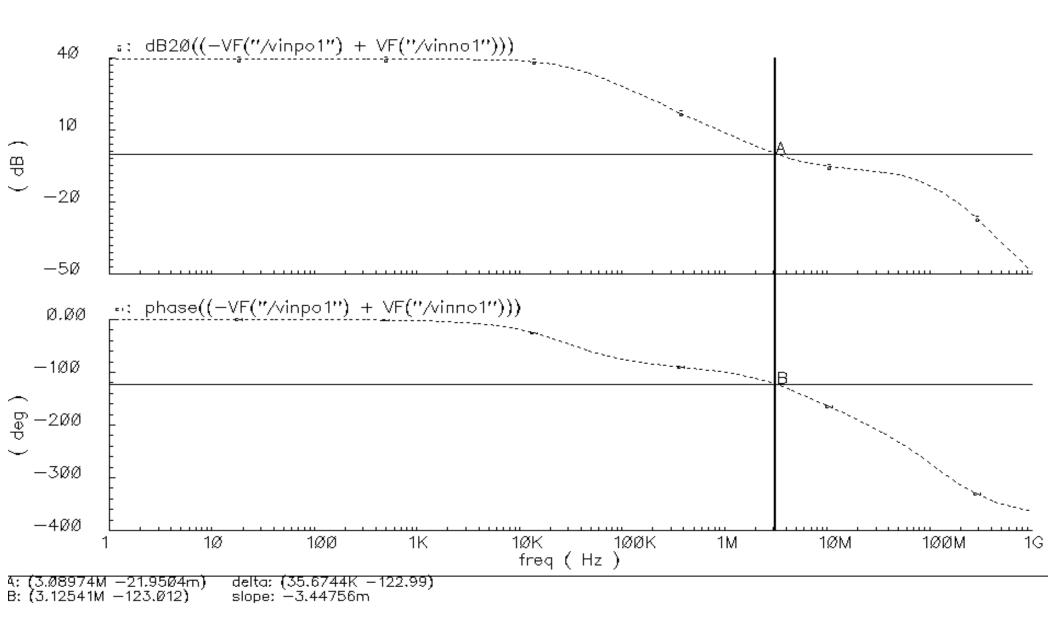

Loop gain simulation Cc=0 F , Phase Margin = 37.86°

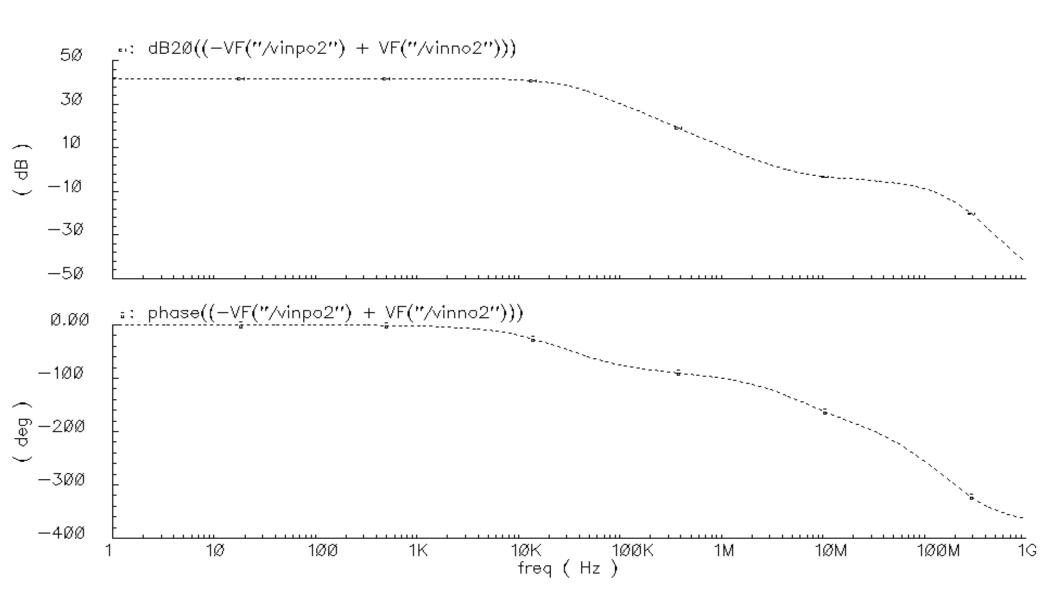

Phase Margin = 47.13° Cc=1pF

#### Cc+R compensation, 1pF+20kOhm Phase Margin = 74.36°

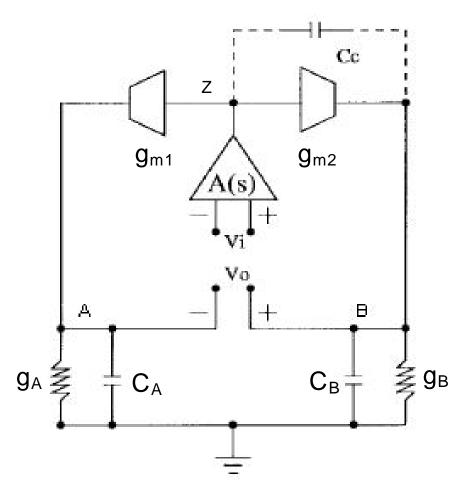

$$A(s) = \frac{A_0}{1 + sC_Z / g_Z}$$

$g_A$  is the total conductance of node A, and  $g_A = g_{o1} + g_A'$ ,

$g_B$  is the total conductance of node B, and  $g_B = g_{o2} + g_B'$ ,

$g_z$  is the total conductance of node Z

$C_A$ ,  $C_B$  and  $C_Z$  are the total capacitance at nodes A, B and Z

Then the open loop transfer function from

$$V_{it/.}$$

to  $V_{ot/.}$  is

$$H_{oL}(s) = \frac{v_o(s)}{v_i(s)} = \frac{A_0 g_m (g_A' - g_B')}{g_o (g_o + g_A')} \times \frac{1 + s(C_A - C_B) / (g_A' - g_B')}{(1 + s / p_A)(1 + s / p_B)(1 + s / p_Z)}$$

$$p_Z = \frac{g_Z}{C_Z}, p_B = \frac{g_B}{C_B} = \frac{(g_o + g_B')}{C_B}, p_A = \frac{g_A}{C_A} = \frac{(g_o + g_A')}{C_A}$$

The transfer function with  $C_c$  in place is

$$H_{oL}(s) = \frac{A_0 g_m (g_A' - g_B')}{(g_o + g_A')(g_o + g_B')} \times \frac{(1 - s_{Z1})(1 + s_{Z2})}{(1 + s / p_A)(1 + s / p_B')(1 + s / p_Z')}$$

$$z_1 = \frac{g_A' - g_B'}{C_C} \times \frac{g_m}{g_m + g_A'}$$

$$p_B' = \frac{g_m}{C_A + C_B}$$

$$z_2 = \frac{g_m}{C_B}$$

$$p_Z' = \frac{g_Z g_o}{g_m C_C}$$

## a nulling resistor $R_c$ can be added in series with $C_c$ to push $z_1$ to higher frequency

$$z_{1} = \frac{1}{CC(1/g_{m} + 1/g_{A}' - R_{C})}$$

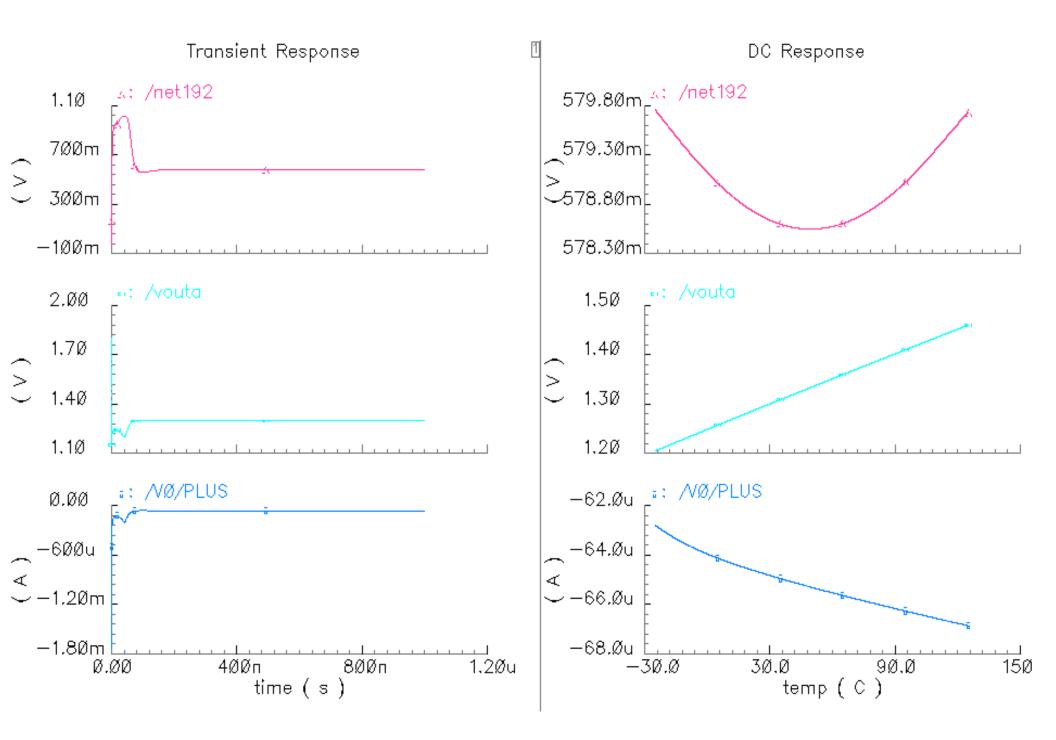

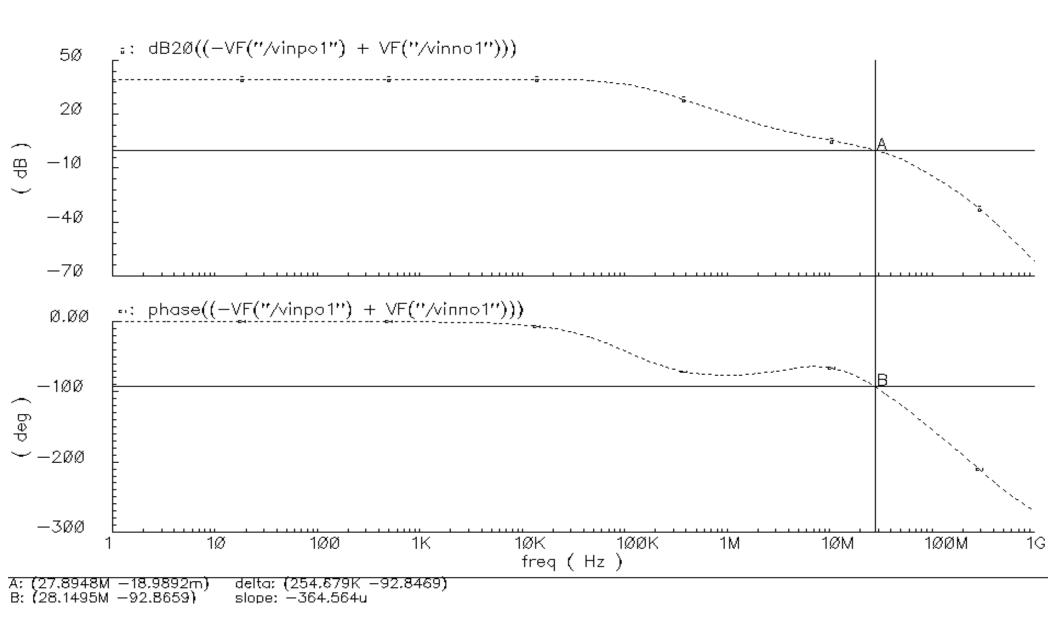

#### **BG Circuit 3 with modified self-biasd circuit**

Reduce one transistor in the self-biased loop to change the type of the feedback

With Cc=0, Phase Margin = 87.13°

Cc=1 pF, Phase Margin = 56.99° Lower bandwidth

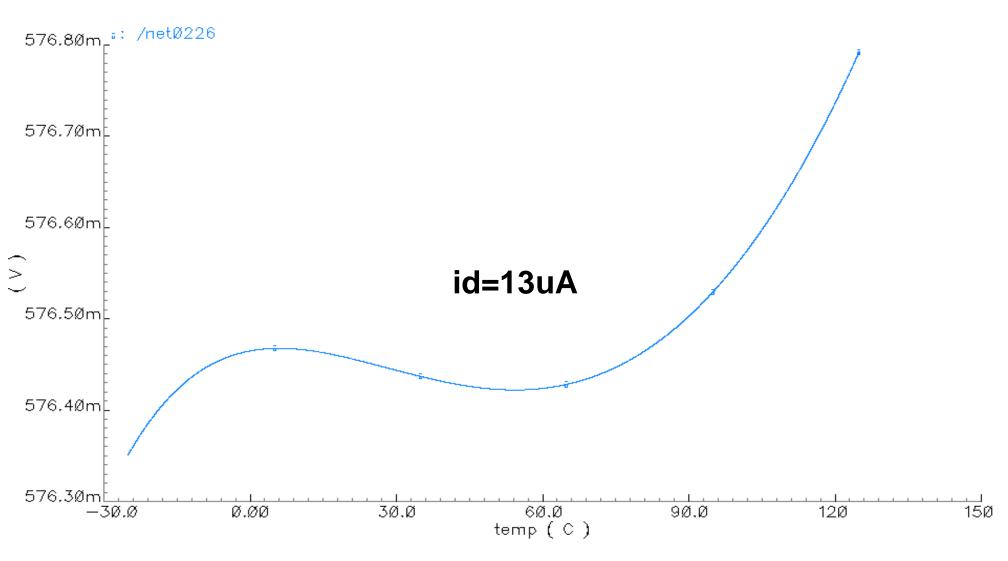

#### **BG Simulation for different diode current**

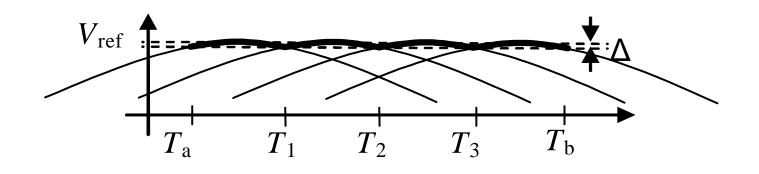

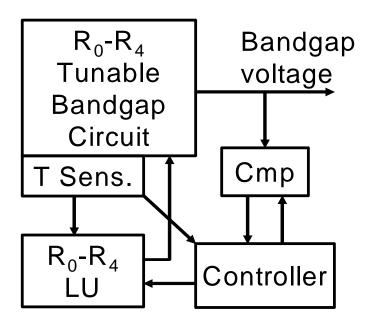

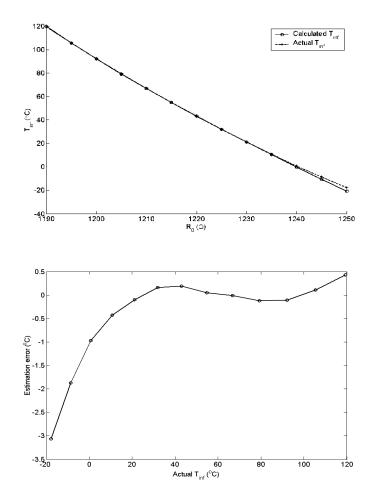

# Characterization of a bandgap circuit